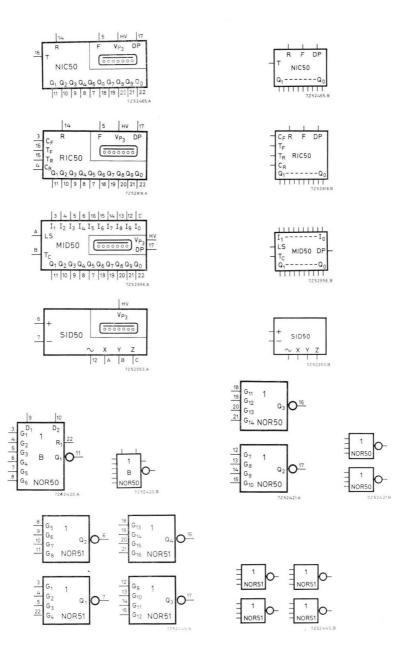

# 50-SERIES DIRECT DISPLAY COUNTERS

# SERVICE CHART

of 50-series direct display counters

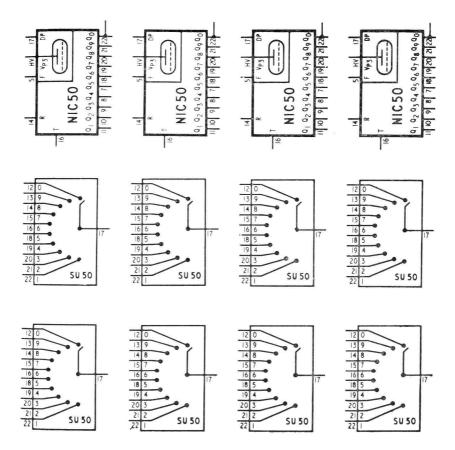

terminal locations

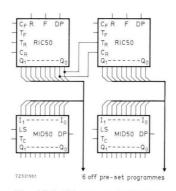

a complete range of modular sub-systems

for preset programmed control

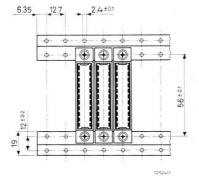

# **Terminal Locations**

| 250V | IHV         |             |    |

|------|-------------|-------------|----|

| 24V  | 11          |             |    |

| OV   | 12          |             |    |

|      |             | 141         | R  |

| F    | 15          | 16 <b>I</b> | т  |

|      |             | 17 I        | DP |

| Qs   | 17          | 18          | 06 |

| Q4   | 18          | 19 [        | Q7 |

| Q3   | 19          | 201         | QB |

| Q2   | 1 10        | 21 1        | Qg |

| Q1   | <b>8</b> 11 | 22          | ao |

|    |      | [HV  | 250V |

|----|------|------|------|

|    |      | 11   | 24V  |

|    |      | 12   | OV   |

| R  | 141  | 13   | CF   |

| TR | 15   | 14   | CR   |

| TF | 16 1 | 15   | F    |

| DF | 17 1 |      |      |

| 06 | 18 [ | 17   | Qs   |

| 07 | 19 [ | 18   | 04   |

| 08 | 201  | 19   | Q3   |

| Qg | 21 1 | 1 10 | Q2   |

| a  | 221  | 1 11 | 01   |

| 250V | IHV  | AI   | LS             |

|------|------|------|----------------|

|      |      | BI   | Tc             |

|      |      | CI   | Io             |

| 24V  | 11   | 12   | Ig             |

| OV   | 12   | 13   | I <sub>8</sub> |

| I1   | 13   | 14   | 17             |

| I2   | 14   | 15   | I6             |

| I3   | 15   | 16   | Is             |

| I4   | 16   | 17 1 | DP             |

| Q5   | 17   | 18   | Q6             |

| 04   | 18   | 19 [ | 07             |

| Q3   | 1 9  | 201  | Q8             |

| Q2   | I 10 | 21   | Qg             |

| Q1   | 1 11 | 22 1 | ao             |

| 24V                                                                   | 11       | 12                  | G <sub>7</sub>                                                                                    | 24V<br>0V                                                                                                  | 11   | 12                   | G <sub>9</sub>                                                           |                              |

|-----------------------------------------------------------------------|----------|---------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|----------------------|--------------------------------------------------------------------------|------------------------------|

| ov                                                                    | 12       | 13                  | G <sub>8</sub><br>G <sub>9</sub>                                                                  | G <sub>1</sub>                                                                                             | 13   | 14                   | G 11                                                                     |                              |

| G <sub>1</sub>                                                        | 14       | 15                  | G <sub>10</sub>                                                                                   | G <sub>2</sub>                                                                                             | 14   | 15                   | G12                                                                      |                              |

| G <sub>2</sub><br>G <sub>3</sub>                                      | 15       | 16                  | Q <sub>3</sub>                                                                                    | G <sub>3</sub>                                                                                             | 15   | 16                   | 04                                                                       |                              |

| G <sub>4</sub>                                                        | 16       | 17                  | Q <sub>2</sub>                                                                                    | Q <sub>2</sub>                                                                                             | 16   | 17 1                 | Q3                                                                       |                              |

| G <sub>5</sub>                                                        |          | 18                  | G <sub>11</sub>                                                                                   | Q <sub>1</sub>                                                                                             | 17   | 18                   | G <sub>13</sub>                                                          |                              |

| G <sub>6</sub>                                                        | 18       | 19                  | G <sub>12</sub>                                                                                   | G <sub>5</sub>                                                                                             | 18   | 19                   | G14                                                                      |                              |

| D <sub>1</sub>                                                        | 19       | 20                  | G <sub>13</sub>                                                                                   | G <sub>6</sub>                                                                                             | 19   | 20 1                 | G 15                                                                     |                              |

| D <sub>2</sub>                                                        | 110      | 21 1                | G <sub>14</sub>                                                                                   | G <sub>7</sub>                                                                                             | 110  | 21                   | G 16                                                                     |                              |

| Q1                                                                    | 1 11     | 22 1                | R <sub>1</sub>                                                                                    | G <sub>8</sub>                                                                                             | 1 11 | 22                   | G4                                                                       |                              |

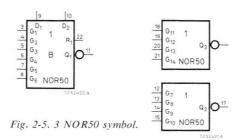

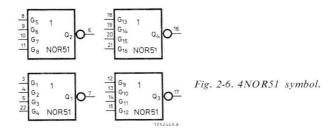

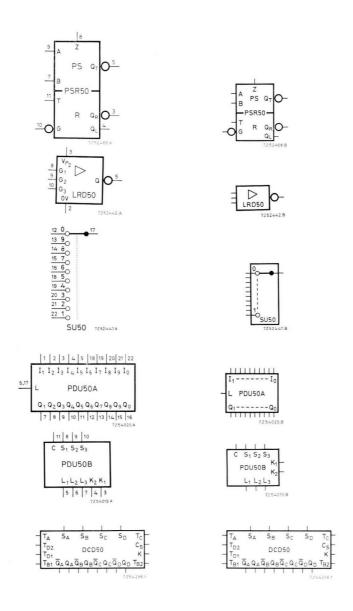

| 5 G <sub>3</sub> D O                                                  | 2        | 18<br>19<br>20<br>2 | G <sub>11</sub> 1<br>G <sub>12</sub> 0 <sub>3</sub> O <sup>15</sup><br>G <sub>14</sub> NOR50      | G <sub>5</sub> 1<br>G <sub>6</sub> 0 <sub>2</sub><br>G <sub>7</sub> 0 <sub>2</sub><br>G <sub>8</sub> NOR51 | 6    | 18<br>19<br>20<br>21 | G <sub>13</sub><br>G <sub>14</sub><br>G <sub>15</sub><br>G <sub>16</sub> | 1<br>Q4<br>NOR51             |

| 6 G <sub>4</sub> B Q <sub>1</sub> G <sub>5</sub> G <sub>6</sub> NOR50 | <b>)</b> | 1:                  | G <sub>1</sub> G <sub>2</sub> G <sub>3</sub> G <sub>2</sub> O <sup>17</sup> G <sub>10</sub> NOR50 | G <sub>1</sub> 1<br>G <sub>2</sub> 0 <sub>1</sub><br>G <sub>3</sub> 0 <sub>1</sub><br>G <sub>4</sub> NOR51 | 7    | 12<br>13<br>14<br>15 | G <sub>9</sub><br>G <sub>10</sub><br>G <sub>11</sub><br>G <sub>12</sub>  | 1<br>Q <sub>3</sub><br>NOR51 |

| I, | 11         | 12   | Q6             |

|----|------------|------|----------------|

| I2 | 12         | 13   | 07             |

| I3 | 13         | 14 1 | Qg             |

| I  | 14         | 15   | Qg             |

| I, | 15         | 16   | Qo             |

| L  | 16         | 17 1 | L              |

| Q1 | <b>F</b> 7 | 18   | I <sub>6</sub> |

| Q2 | 18         | 19 [ | I7             |

| Q3 | 19         | 20   | Is             |

| Q4 | 110        | 21   | Ig             |

| Qs | 1 11       | 22   | Io             |

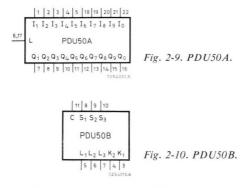

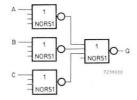

| 11             | 2   3   4   5   18   19   20   21   2                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Iı             | 1 <sub>2</sub> I <sub>3</sub> I <sub>4</sub> I <sub>5</sub> I <sub>8</sub> I <sub>9</sub> 2 <sub>0</sub> 2 <sub>1</sub> 2 <sub>2</sub> I <sub>2</sub> I <sub>3</sub> I <sub>4</sub> I <sub>5</sub> I <sub>6</sub> I <sub>7</sub> I <sub>8</sub> I <sub>9</sub> I <sub>0</sub> |

| L              | PDU50A                                                                                                                                                                                                                                                                        |

| Q <sub>1</sub> | Q2Q3Q4Q5Q6Q7Q8Q9Q0                                                                                                                                                                                                                                                            |

|      | I <sub>1</sub> I <sub>2</sub> | 3 4 5 18 19 20 21 2<br>I <sub>3</sub> I <sub>4</sub> I <sub>5</sub> I <sub>6</sub> I <sub>7</sub> I <sub>8</sub> I <sub>9</sub> I <sub>0</sub> | ٦ |

|------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 6,17 | L                             | PDU50A                                                                                                                                         | ١ |

|      | Q1 Q2                         | Q <sub>3</sub> Q <sub>4</sub> Q <sub>5</sub> Q <sub>6</sub> Q <sub>7</sub> Q <sub>8</sub> Q <sub>9</sub> Q <sub>0</sub>                        |   |

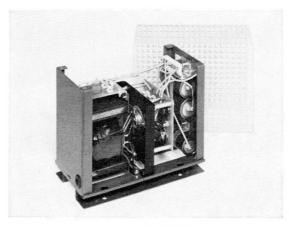

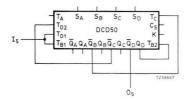

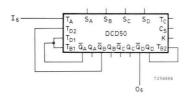

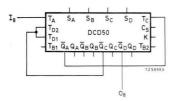

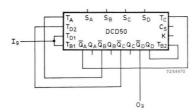

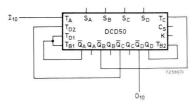

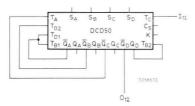

|      | 15                                    | 12      | 10                            | 11              |     |

|------|---------------------------------------|---------|-------------------------------|-----------------|-----|

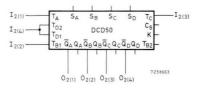

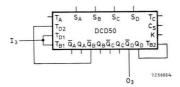

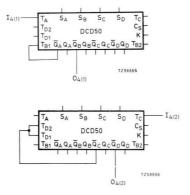

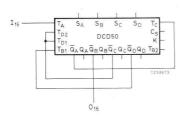

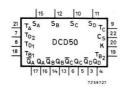

| 21 T | SA                                    | SB      | Sc                            | SD TC           | 9   |

| 8 T  | D <sub>2</sub>                        | DCI     | 050                           | C <sub>S</sub>  | 20  |

| 18 T | B1<br>Q <sub>A</sub> Q <sub>A</sub> ( | Q Q Q R | ā <sub>c</sub> a <sub>c</sub> | T <sub>B2</sub> | 19  |

|      | 17 16                                 | 14 13   | 6 5                           | 3 4             |     |

|      |                                       |         |                               | 7258727         | ii. |

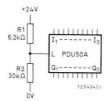

| 244            | 11          |  |

|----------------|-------------|--|

| 0              | 12          |  |

| K <sub>1</sub> | 13          |  |

| K <sub>2</sub> | 14          |  |

| L1             | 15          |  |

| L2             | 16          |  |

| L <sub>3</sub> | 17          |  |

| 51             | 18          |  |

| 52             | 19          |  |

| 53             | <b>I</b> 10 |  |

| C              | I 11        |  |

| 1 | 1 8 9 10                                     |

|---|----------------------------------------------|

| C | S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> |

|   | PDU50B                                       |

|   | L1 L2 L3 K2 K1                               |

|   | 5 6 7 4 3                                    |

|   | 72587                                        |

**50-Series Direct Display Counters**

# © N.V. Philips' Gloeilampenfabrieken EINDHOVEN - The Netherlands June 1970

The publication of this document does not imply a licence under any patent

# **50-Series Direct Display Counters**

edited by J. Deerson

PUBLICATIONS DEPARTMENT

ELECTRONIC COMPONENTS AND MATERIALS DIVISION

# **Contents**

# Preface

| Int | roduct | ion         |                    |      |     |      |      |     |     |     |     |     |     |    |   | • |   |  | 1  |

|-----|--------|-------------|--------------------|------|-----|------|------|-----|-----|-----|-----|-----|-----|----|---|---|---|--|----|

|     |        | How to      | o use this book    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 1  |

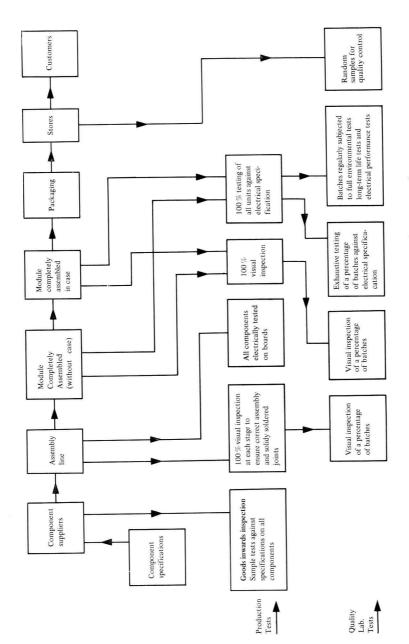

|     | -      | Quality     | y control and envi | ron  | me  | nta  | 1 to | est | spe | eci | fic | ati | ior | ıs |   |   |   |  | 2  |

|     | _      | Applic      | ations             |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 2  |

|     |        |             |                    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  |    |

| Pa  | rt 1   | General 1   | Design Philosophy  |      |     |      |      |     |     |     |     |     |     |    | , |   |   |  | 5  |

| 1   | Chara  | acteristics |                    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 7  |

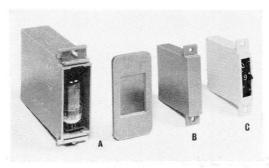

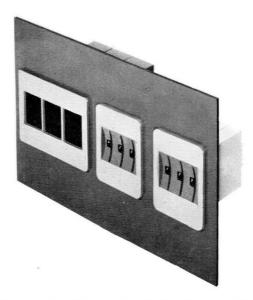

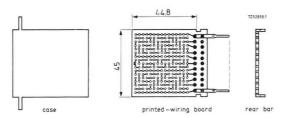

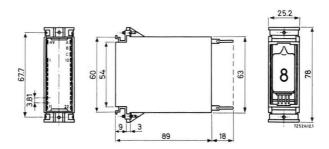

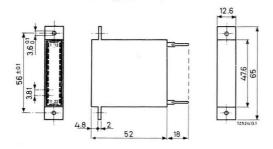

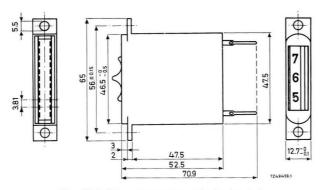

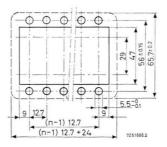

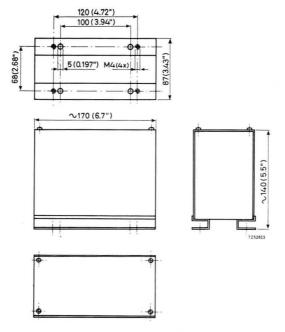

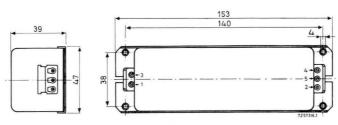

|     | 1.1    | Physical    | characteristics    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 7  |

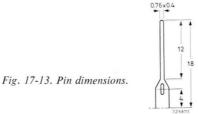

|     |        | 1.1.1       | Pin connections    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 7  |

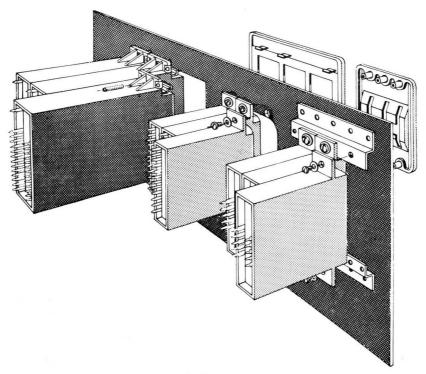

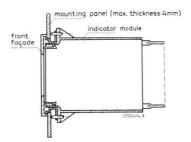

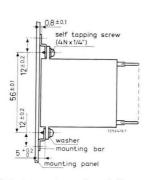

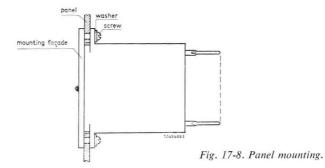

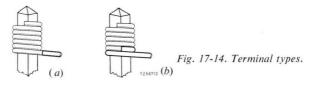

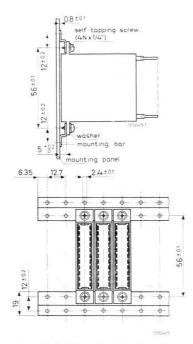

|     |        | 1.1.2       | Mounting           |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 7  |

|     | 1.2    | Electrica   | al characteristics |      |     |      |      |     |     |     |     |     |     |    | ٠ |   |   |  | 8  |

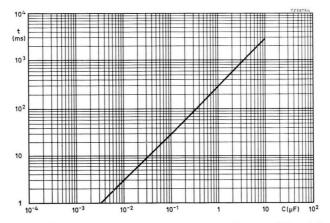

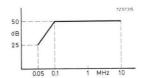

|     |        | 1.2.1       | Counting rate      |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 8  |

|     |        | 1.2.2       | Temperature rang   | e    |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 8  |

|     |        | 1.2.3       | Supply voltage     |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 8  |

| 2   | Func   | tional De   | scription          |      | į.  |      |      |     |     |     |     |     |     |    |   |   |   |  | 9  |

|     | 2.1    | Display     | modules            |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 9  |

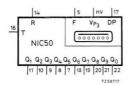

|     |        | 2.1.1       | Numerical Indica   |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 9  |

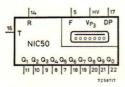

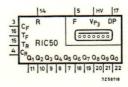

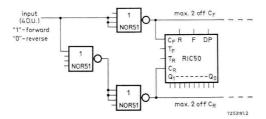

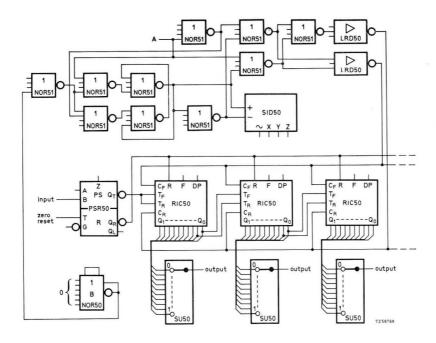

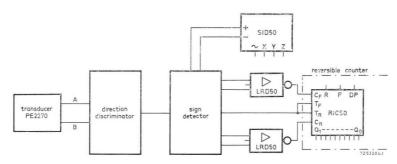

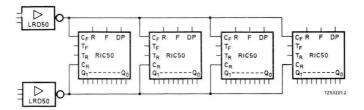

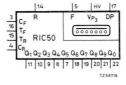

|     |        | 2.1.2       | Reversible Indica  | tor  | Co  | un   | ter  | R   | IC: | 50  |     |     |     |    |   |   |   |  | 9  |

|     |        | 2.1.3       | Memory Indicato    | r D  | riv | er   | M    | D   | 50  |     |     |     |     |    |   |   |   |  | 9  |

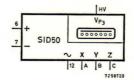

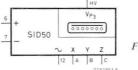

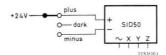

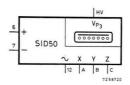

|     |        | 2.1.4       | Sign Indicator Dr  | ive  | r S | ID   | 50   |     |     |     |     |     |     |    |   |   |   |  | 10 |

|     | 2.2    | Auxilian    | ry and logic modu  | les  |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 10 |

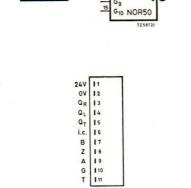

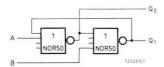

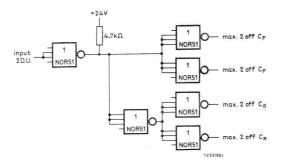

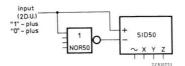

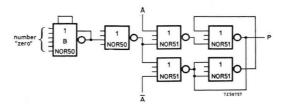

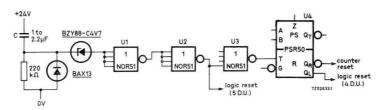

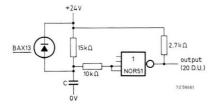

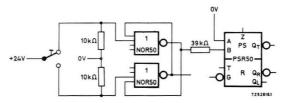

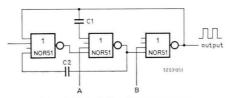

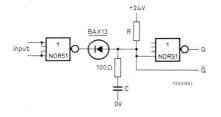

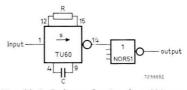

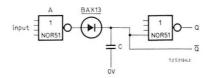

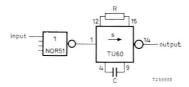

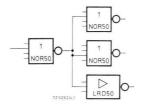

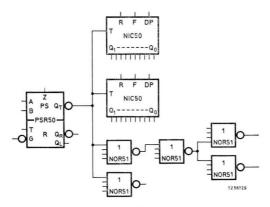

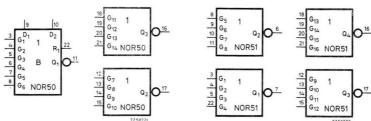

|     |        | 2.2.1       | Triple NOR mod     |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 10 |

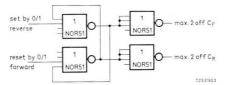

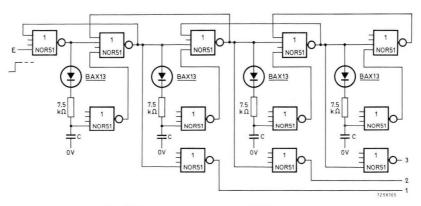

|     |        | 2.2.2       | Ouadruple NOR      | mo   | du  | le 4 | N    | OR  | 51  |     |     |     |     |    |   |   |   |  | 11 |

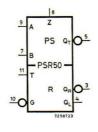

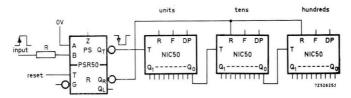

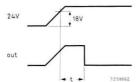

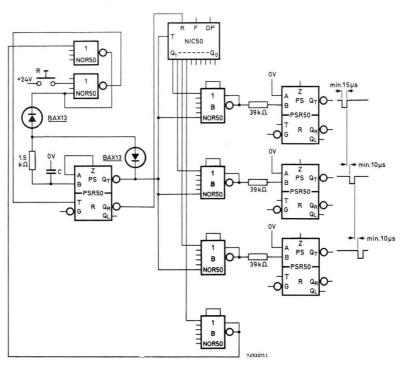

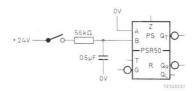

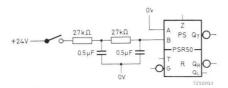

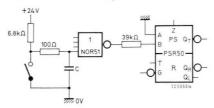

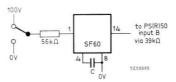

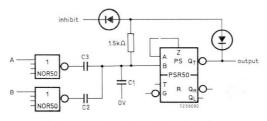

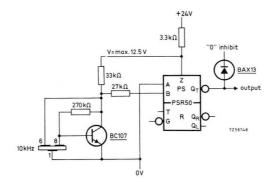

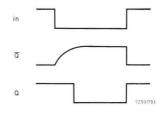

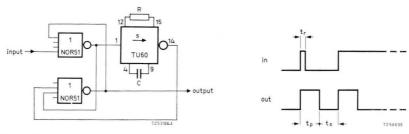

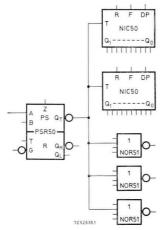

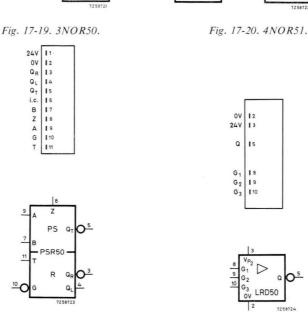

|     |        | 2.2.3       | Pulse Shaper-Res   | et r | no  | dul  | e P  | SR  | 50  |     |     |     |     |    |   |   |   |  | 11 |

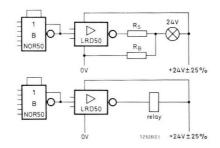

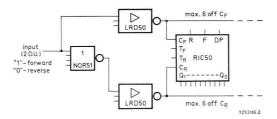

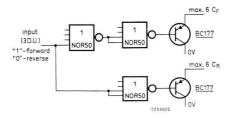

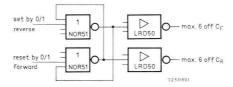

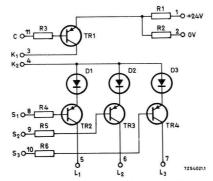

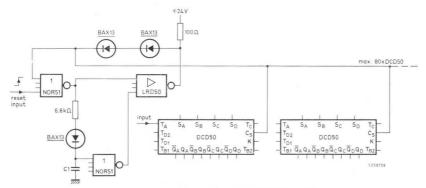

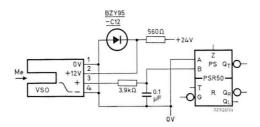

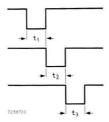

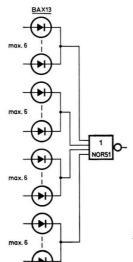

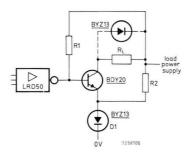

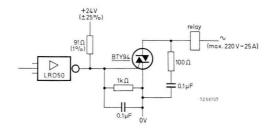

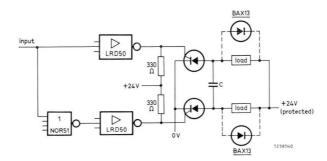

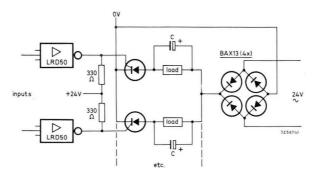

|     |        | 2.2.4       | Lamp-Relay Driv    | er   | LR  | D5   | 0    |     |     |     |     |     |     |    |   |   |   |  | 11 |

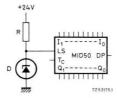

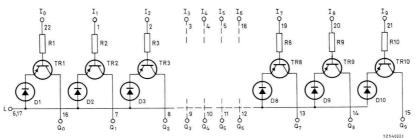

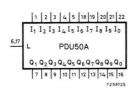

|     |        | 2.2.5       | Printer Drive mo   | dul  | es  | PD   | U5   |     |     |     |     |     |     |    |   |   |   |  | 12 |

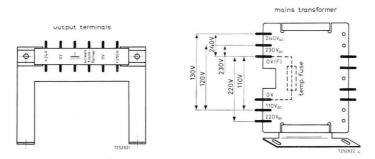

|     |        | 2.2.6       | Power Supply mo    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 12 |

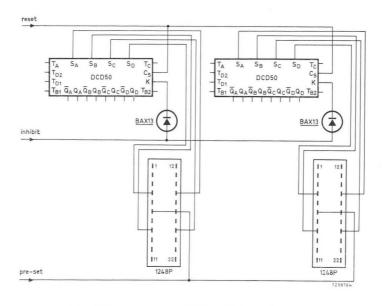

|     |        | 2.2.7       | Decade Counter     | and  | D   | ivio | ler  | D   | CD  | )5( | )   |     |     |    |   |   |   |  | 13 |

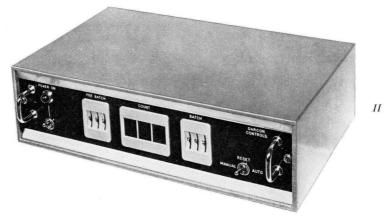

|     | 2.3    | The Sw      | itch Unit          |      |     | •    |      |     |     |     |     |     |     |    |   |   |   |  | 13 |

|     | 2.4    | Accesso     |                    |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 14 |

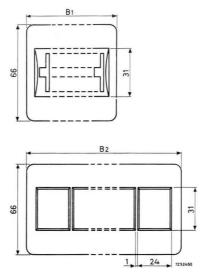

|     |        | 2.4.1       | The Empty Case     | Ass  | en  | ibly | E    | CA  | 150 | )   |     |     |     |    |   |   |   |  | 14 |

|     |        | 2.4.2       | Other accessories  |      |     |      |      |     | ٠   |     |     |     |     |    |   |   |   |  | 14 |

| 3   | Drav   | ving Syml   | bols               |      |     |      |      |     |     |     |     |     |     |    |   |   | , |  | 15 |

|     | 3.1    | "Sticke     | r'' symbols        |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 15 |

|     | 3.2    |             | tic symbols        |      |     |      |      |     |     |     |     |     |     |    |   |   |   |  | 15 |

| 4  | The   | 50-Series Design Philosophy                           | 3 |

|----|-------|-------------------------------------------------------|---|

|    | 4.1   | Counting                                              | 3 |

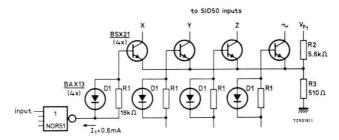

|    | 4.2   | Interfacing with the logic                            | 3 |

|    | 4.3   | The logic system                                      | 3 |

|    | 4.4   | Output drive                                          | ) |

|    | 4.5   | Input requirements                                    | ) |

|    | 4.6   | Additional modules                                    |   |

| Pa | rt 2  | Counting Circuits                                     | 3 |

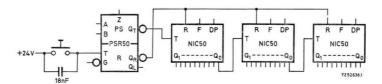

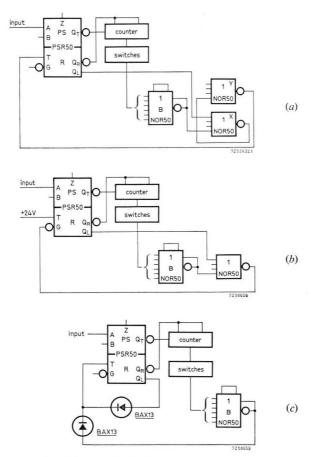

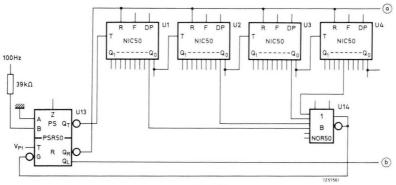

| 5  | Uni-  | directional Counting with the NIC50                   | 5 |

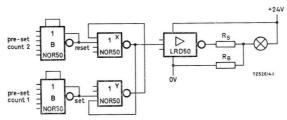

|    | 5.1   | Counting with pre-determined outputs                  | 7 |

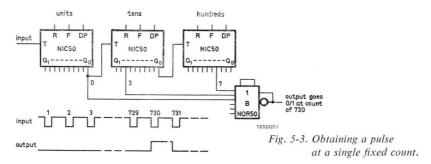

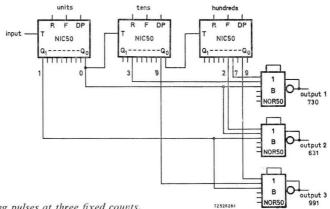

|    |       | 5.1.1 Fixed pre-determined outputs                    | 7 |

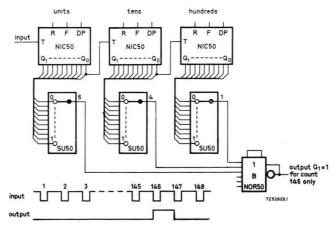

|    |       | 5.1.2 Variable preset outputs                         | 3 |

|    | 5.2   | Using the pre-determined outputs                      | 3 |

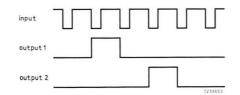

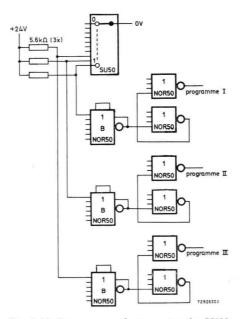

|    |       | 5.2.1 Direct output drive                             | 3 |

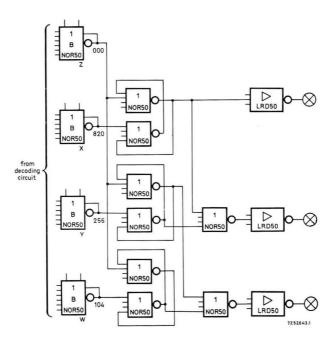

|    |       | 5.2.2 Output drive via intermediate logic             | ) |

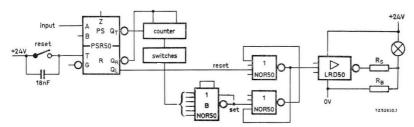

|    |       | 5.2.3 Resetting                                       | L |

|    |       | 5.2.4 A typical example                               | L |

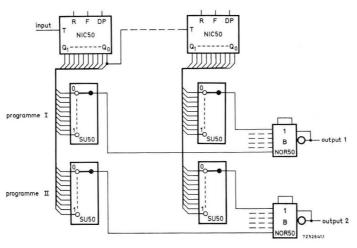

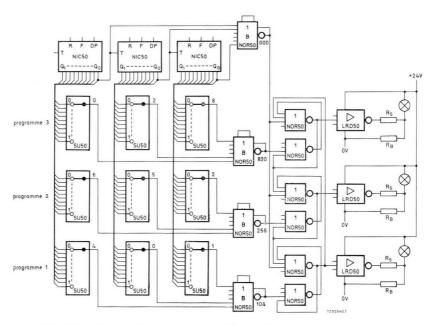

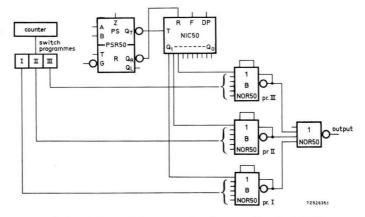

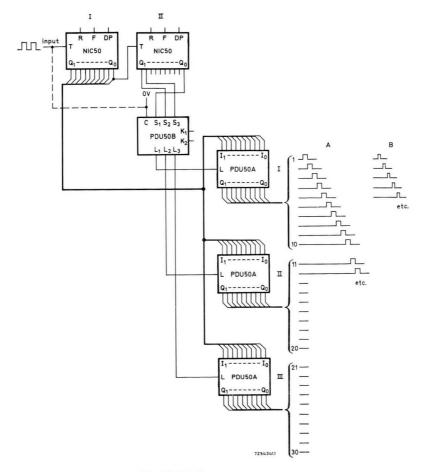

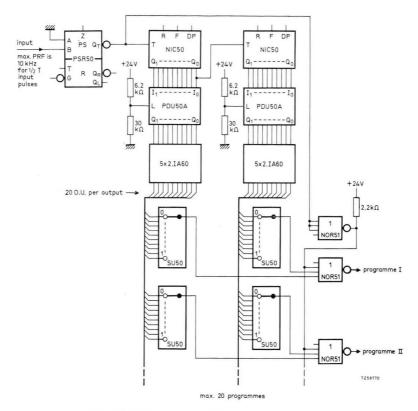

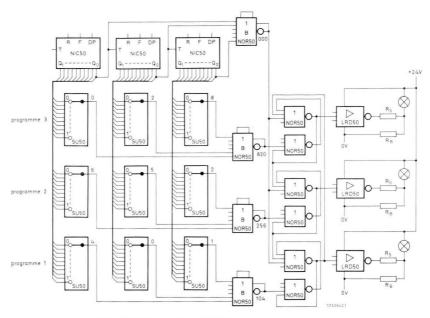

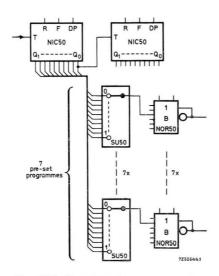

|    | 5.3   | Sequential programme selection                        | 2 |

|    |       | 5.3.1 Selection with NIC50                            | 2 |

|    |       | 5.3.2 Selection with SU50                             | 2 |

|    | 5.4   | Variable scaling                                      |   |

|    | 5.5   | Decimal point indication                              | ļ |

| 6  | Bi-di | rectional Counting with the RIC50                     | 5 |

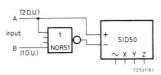

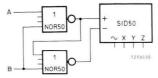

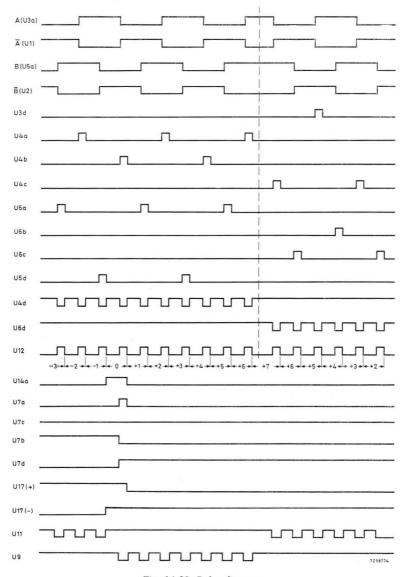

|    | 6.1   | Various methods of controlling counting direction     | , |

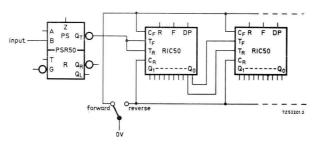

|    |       | 6.1.1 Control with a single input and a switch        | í |

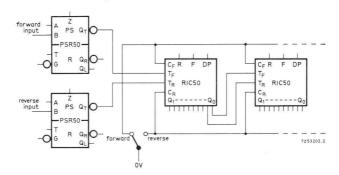

|    |       | 6.1.2 Control with separate inputs and a switch       | , |

|    |       | 6.1.3 Control by logic                                |   |

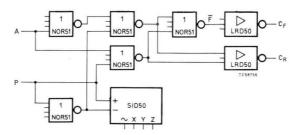

|    | 6.2   | Counting with pre-determined outputs                  |   |

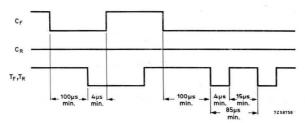

|    | 6.3   | Special requirements of input signal relationship     |   |

|    |       |                                                       |   |

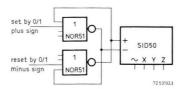

| 7  | Sign  | Indication with the SID50                             | , |

|    | 7.1   | Driving the $+$ and $-$ signs                         | ) |

|    |       | 7.1.1 Switched inputs drive                           | , |

|    |       | 7.1.2 Logic drive                                     | 1 |

|    | 7.2   | Sign indication and counting direction control        |   |

|    | 7.3   | A typical example                                     |   |

|    | 7.4   | Driving the X, Y, Z, and $\sim$ signs in the SID50 44 | , |

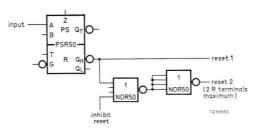

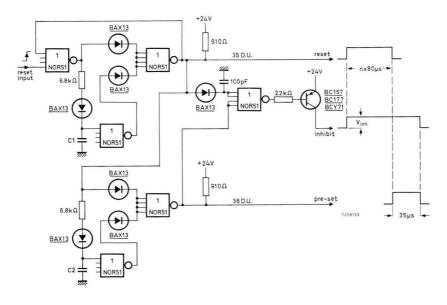

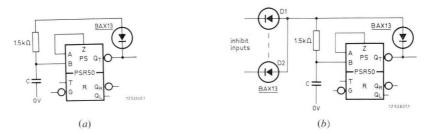

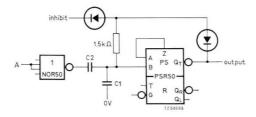

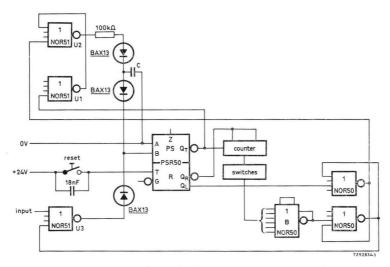

| 8  | Reset | ting the System with the PSR50                        |   |

|    | 8.1   | General                                               |   |

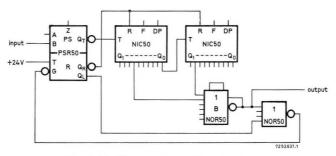

|    | 82.   | Normal resetting                                      |   |

|    |       | 8.2.1 Manual resetting                                |   |

|    |       | 8.2.2 Resetting at a pre-determined count             |   |

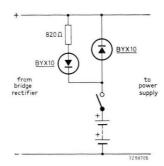

|    |       | 13.8.4                                                                                                                            | Thyristor drive                                                                                           |     |         | 112                                                                              |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|---------|----------------------------------------------------------------------------------|

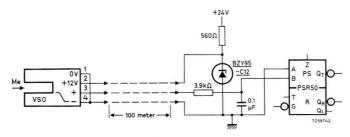

|    | 13.9  |                                                                                                                                   | distance input signal transmission (over 100 m)                                                           |     |         | 113                                                                              |

|    |       |                                                                                                                                   | hift and decimal point shift                                                                              |     |         | 114                                                                              |

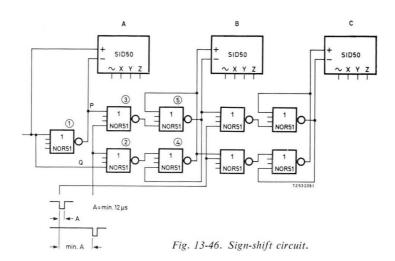

|    | 13.10 |                                                                                                                                   | I Sign shift with SID50                                                                                   |     |         | 114                                                                              |

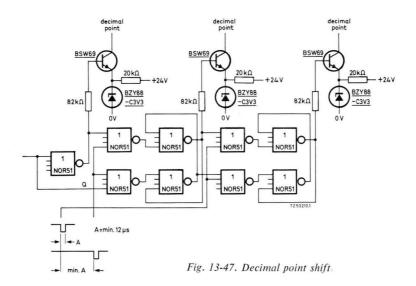

|    |       | 13.10.1                                                                                                                           | 2 Decimal point shift                                                                                     |     |         | 115                                                                              |

|    |       |                                                                                                                                   |                                                                                                           |     |         |                                                                                  |

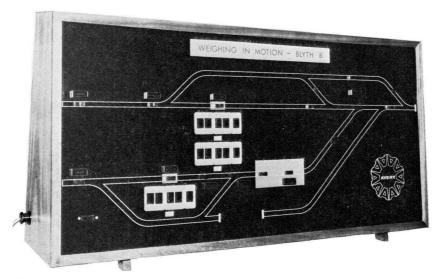

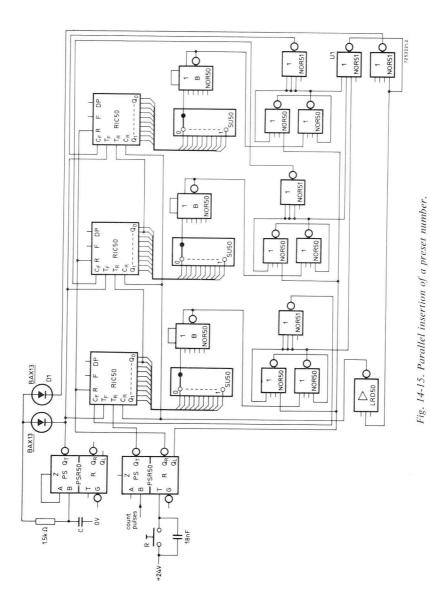

| 14 | Exam  | ples of V                                                                                                                         | Virtually Complete Systems                                                                                |     |         | 116                                                                              |

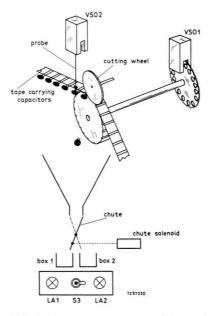

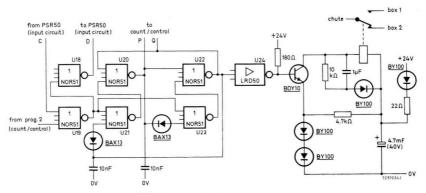

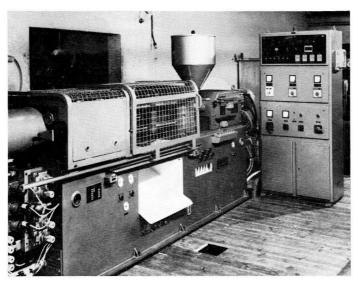

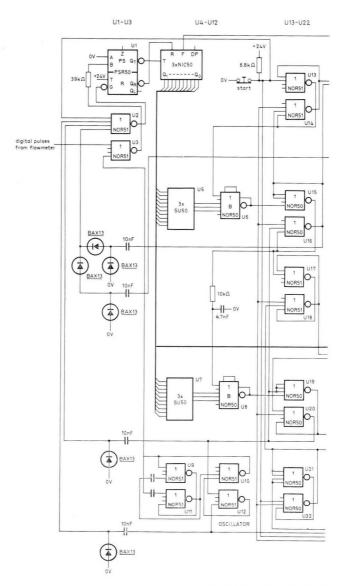

|    | 14.1  |                                                                                                                                   | nting system for batching of components                                                                   |     |         | 116                                                                              |

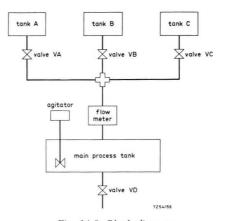

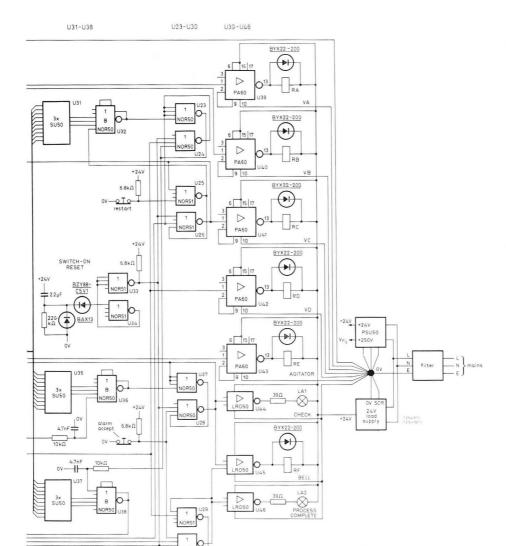

|    | 14.2  | Chemic                                                                                                                            | cal blending plant control                                                                                |     |         | 124                                                                              |

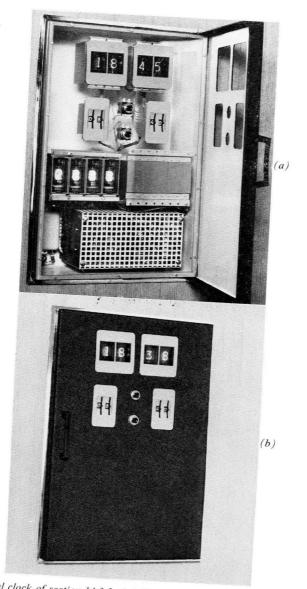

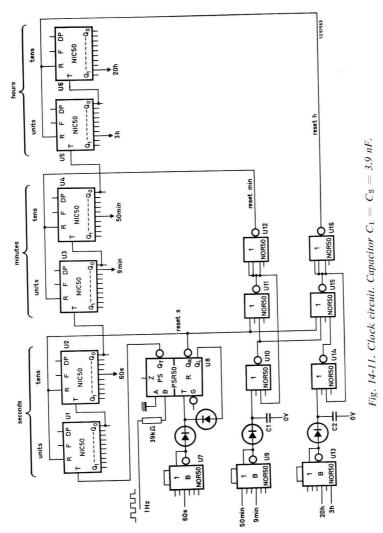

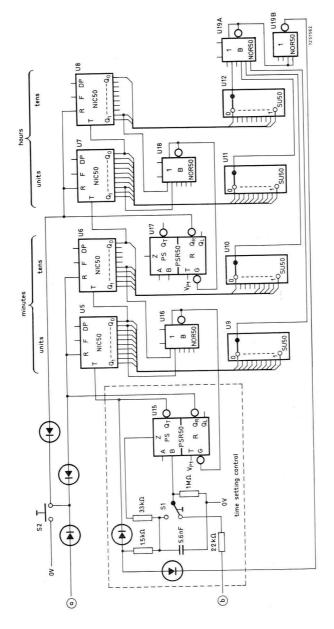

|    | 14.3  |                                                                                                                                   | circuits                                                                                                  |     |         | 132                                                                              |

|    |       | 14.3.1                                                                                                                            |                                                                                                           |     |         | 132                                                                              |

|    |       | 14.3.2                                                                                                                            | Clock with manual setting facility                                                                        |     |         | 135                                                                              |

|    | 14.4  | Serial in                                                                                                                         | insertion of count pulses                                                                                 |     |         | 136                                                                              |

|    | 14.5  | Insertio                                                                                                                          | on of preset numbers                                                                                      |     |         | 138                                                                              |

|    |       | 14.5.1                                                                                                                            | Serial insertion                                                                                          |     |         | 138                                                                              |

|    |       | 14.5.2                                                                                                                            | Parallel insertion                                                                                        |     |         | 139                                                                              |

|    | 14.6  | Count                                                                                                                             | position detection                                                                                        |     |         | 139                                                                              |

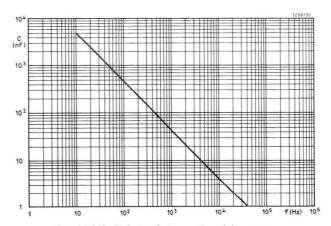

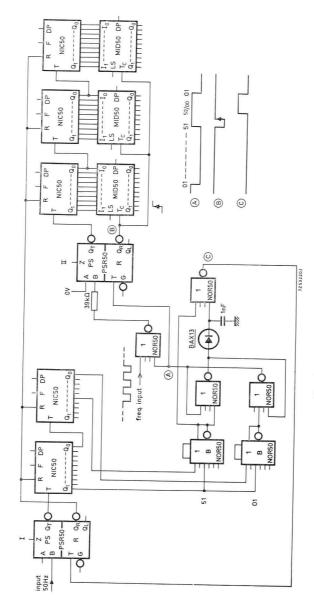

|    | 14.7  |                                                                                                                                   | ency measuring circuit                                                                                    |     |         | 139                                                                              |

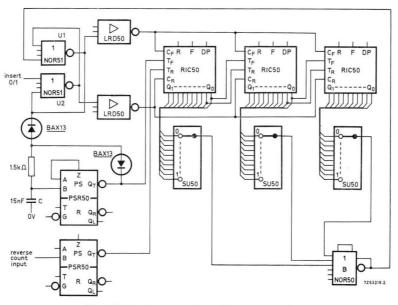

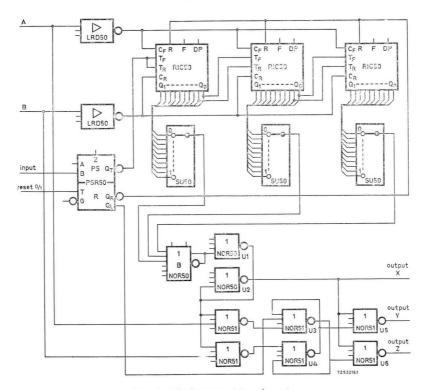

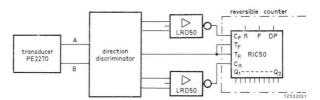

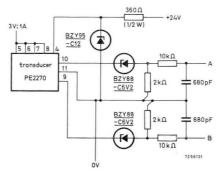

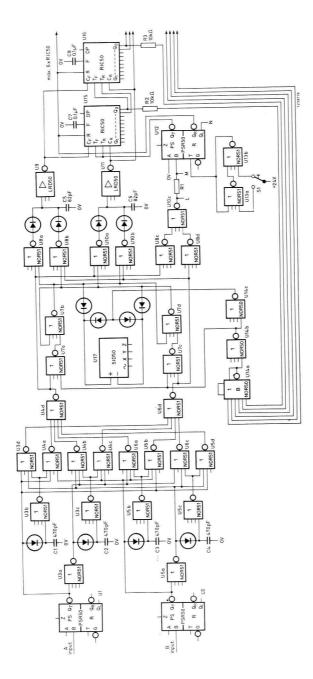

|    | 14.8  | Automa                                                                                                                            | natic bi-directional revolution counting                                                                  |     |         | 143                                                                              |

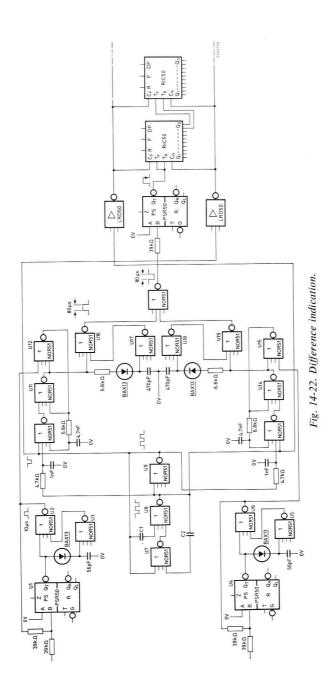

|    | 14.9  |                                                                                                                                   | tion of difference between two independent pulse sources                                                  |     |         | 148                                                                              |

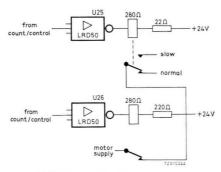

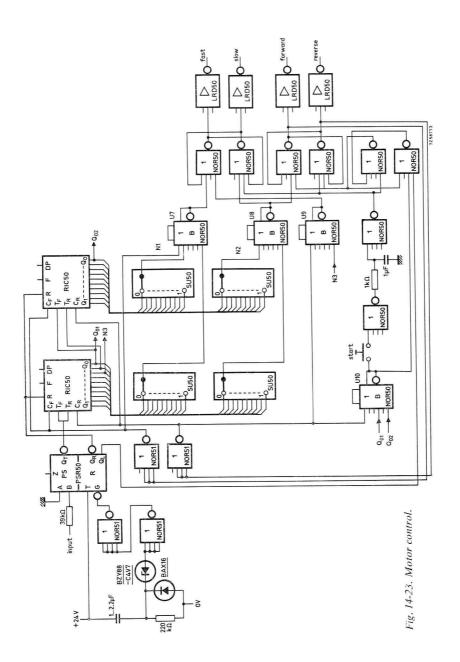

|    | 14.10 | Automa                                                                                                                            | natic motor control                                                                                       |     |         | 150                                                                              |

| Pa | rt 3  | Practica                                                                                                                          | al Considerations                                                                                         |     |         | 153                                                                              |

|    |       |                                                                                                                                   |                                                                                                           |     |         |                                                                                  |

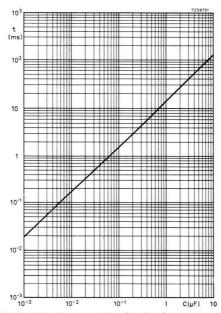

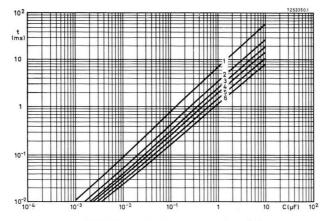

| 15 | Oper  | ating Spo                                                                                                                         | peed                                                                                                      |     | ٠       | 155                                                                              |

| 16 | Load  | ing Table                                                                                                                         | le                                                                                                        |     |         | 159                                                                              |

|    | 16.1  | Rules g                                                                                                                           | governing loading of the modules                                                                          |     |         | 159                                                                              |

|    | 16.2  | _                                                                                                                                 | ading table                                                                                               |     |         | 160                                                                              |

|    | 16.3  | Exampl                                                                                                                            |                                                                                                           |     |         | 162                                                                              |

|    |       | 16.3.1                                                                                                                            | NOR driving 2 × NOR51 plus 1 × LRD50                                                                      |     |         | 160                                                                              |

|    |       | 16.3.2                                                                                                                            |                                                                                                           |     |         | 162                                                                              |

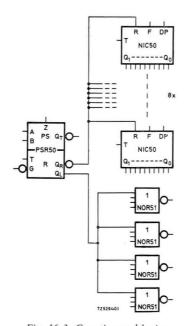

|    |       |                                                                                                                                   | PSR50 driving $3 \times NOR51$ plus $2 \times NIC50$                                                      |     |         | 162                                                                              |

|    |       |                                                                                                                                   | PSR50 driving $3 \times NOR51$ plus $2 \times NIC50$ PSR50 driving $8 \times NIC50$ plus $4 \times NOR51$ |     |         |                                                                                  |

|    |       | 16.3.3<br>16.3.4                                                                                                                  | PSR50 driving 3 × NOR51 plus 2 × NIC50 PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50     |     |         | 162                                                                              |

|    |       | 16.3.3                                                                                                                            | PSR50 driving 8 $\times$ NIC50 plus 4 $\times$ NOR51                                                      |     |         | 162<br>164                                                                       |

|    |       | 16.3.3<br>16.3.4                                                                                                                  | PSR50 driving $8 \times NIC50$ plus $4 \times NOR51$ LRD50 driving the RIC50                              |     |         | 162<br>164<br>164                                                                |

| 17 | Cono  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6                                                                                              | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166                                                  |

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6                                                                                              | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166                                                  |

| 17 | Gene  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta                                                                                 | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166<br>168                                           |

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount:<br>17.1.1                                                             | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166                                                  |

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta                                                                                 | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166<br>168<br>168                                    |

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2                                                    | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166<br>168<br>168                                    |

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2                                                    | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            | D50 | <br>050 | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171                      |

| 17 | 17.1  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2                                                    | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            | D50 | )50<br> | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171<br>174               |

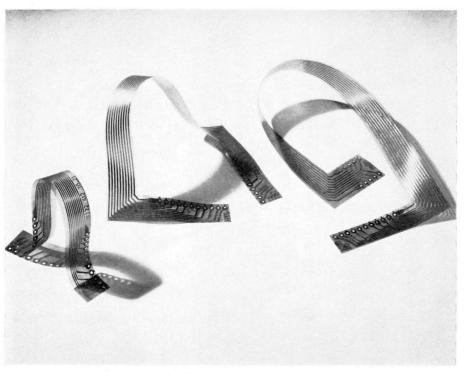

| 17 |       | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>Mount<br>17.1.1<br>17.1.2<br>17.1.3<br>17.1.4<br>Interwi                                  | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            |     |         | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171<br>174<br>175        |

| 17 | 17.1  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2<br>17.1.3<br>17.1.4<br>Interwi<br>17.2.1           | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            | D50 |         | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171<br>174<br>175        |

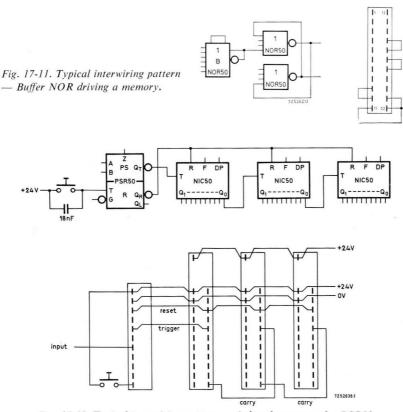

| 17 | 17.1  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2<br>17.1.3<br>17.1.4<br>Interwi<br>17.2.1<br>17.2.2 | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            | D50 | 550     | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171<br>174<br>175<br>175 |

| 17 | 17.1  | 16.3.3<br>16.3.4<br>16.3.5<br>16.3.6<br>ral Insta<br>Mount<br>17.1.1<br>17.1.2<br>17.1.3<br>17.1.4<br>Interwi<br>17.2.1           | PSR50 driving 8 × NIC50 plus 4 × NOR51 LRD50 driving the RIC50                                            | D50 | 50      | 162<br>164<br>164<br>165<br>166<br>168<br>168<br>170<br>171<br>174<br>175        |

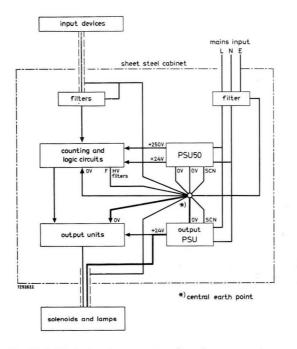

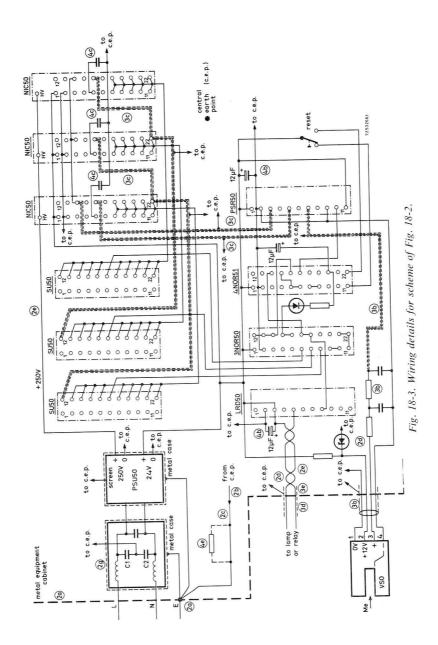

| 18 | Gene  | ral Ele   | ctrical Co | nside  | rat  | ions |      |     |      |      |     | • |   |  |  |  |   |  | 183 |

|----|-------|-----------|------------|--------|------|------|------|-----|------|------|-----|---|---|--|--|--|---|--|-----|

|    | 18.1  | Introd    | duction .  |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  | 183 |

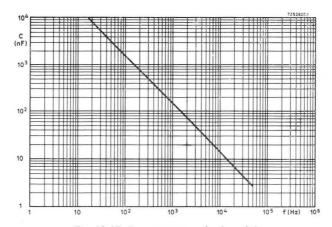

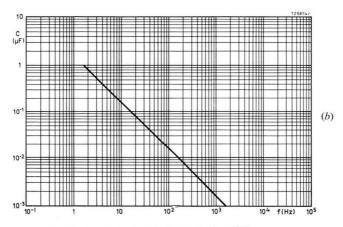

|    | 18.2  | Preca     | utions ag  | ainst  | int  | erfe | ren  | ce  |      |      |     |   |   |  |  |  |   |  | 184 |

|    |       | 18.2.1    | Genera     | al .   |      |      |      |     |      | ٠.   |     |   | × |  |  |  |   |  | 184 |

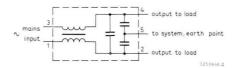

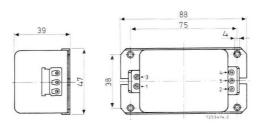

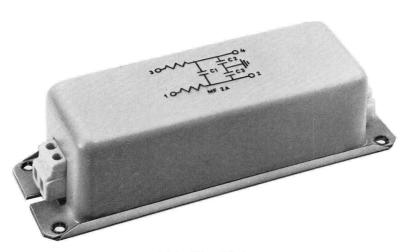

|    |       | 18.2.2    | Norma      | l inte | erfe | eren | ce j | ore | cat  | itic | ns  |   |   |  |  |  |   |  | 185 |

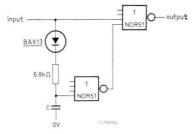

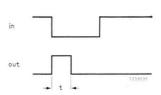

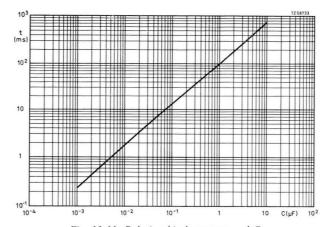

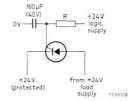

|    |       | 18.2.3    | High in    | nterfe | erei | nce  | pre  | cau | itio | ns   |     |   |   |  |  |  |   |  | 188 |

|    |       | 18.2.4    | Extren     | ne int | erf  | eren | ce   | pre | cai  | atio | ons | 5 |   |  |  |  |   |  | 188 |

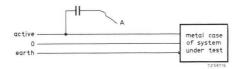

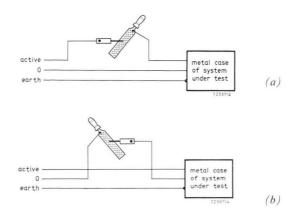

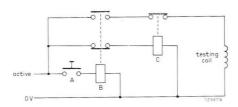

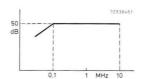

|    |       | 18.2.5    | Test m     | etho   | ds   |      |      |     |      |      |     |   |   |  |  |  |   |  | 189 |

|    |       | 18.2.6    |            |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  |     |

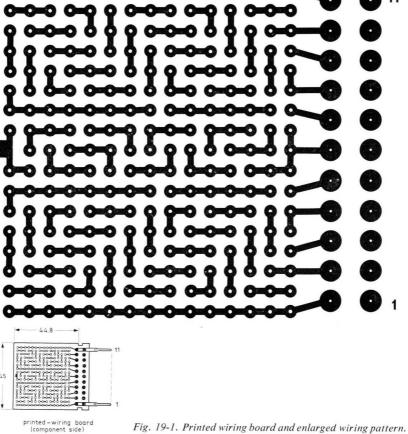

| 19 | Acces | ssories . | · · · · ·  |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  | 196 |

|    | 19.1  | The E     | Empty Cas  | se As  | ser  | nbly | , E  | CA  | 150  |      |     |   |   |  |  |  |   |  | 196 |

|    | 19.2  |           | r symbols  |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  | 196 |

|    | 19.3  |           | ting bar   |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  | 199 |

|    | 19.4  |           | facades    |        |      |      |      |     |      |      |     |   |   |  |  |  |   |  | 200 |

|    | Index | ζ,        |            |        |      | ٠.   |      |     |      |      |     |   |   |  |  |  | , |  | 201 |

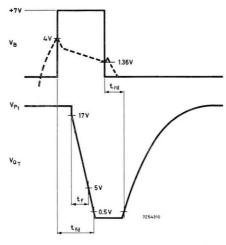

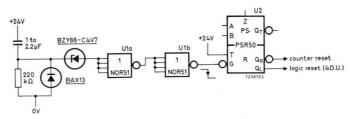

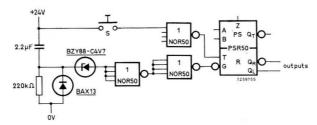

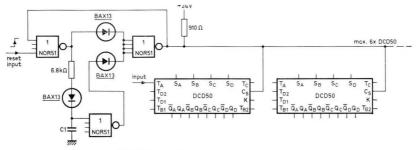

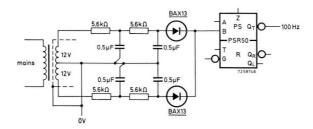

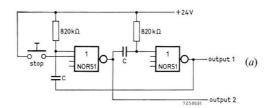

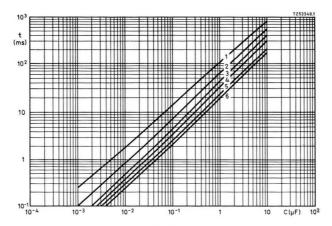

|       | 8.3          | 8.3.1 Resetting at mains switch-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48<br>48 |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       |              | 8.3.2 "Mains switch-on" resetting and manual control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48       |

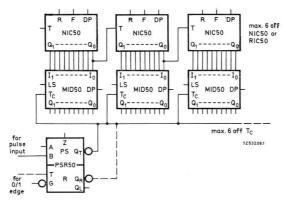

| 9     | Infor        | mation Storage with the MID50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50       |

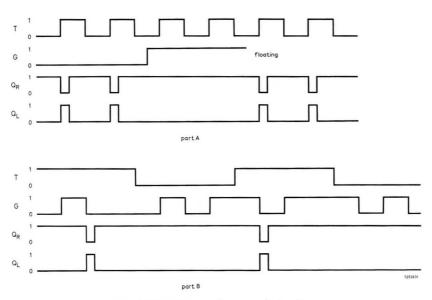

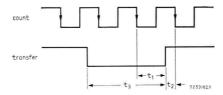

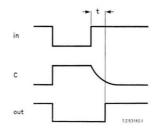

|       | 9.1          | Transfer of information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50       |

|       | 9.2          | Transition of the contract of  | 50       |

|       | 9.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52       |

|       | 9.4          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52       |

|       | 9.5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53       |

| 10112 |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 10    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54       |

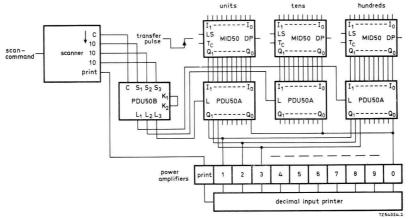

|       | 10.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54       |

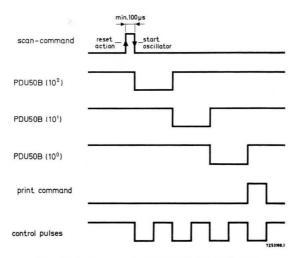

|       | 10.2         | The state of the s | 54       |

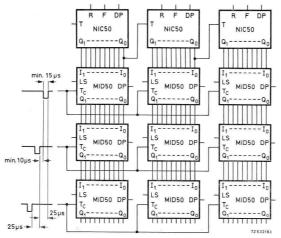

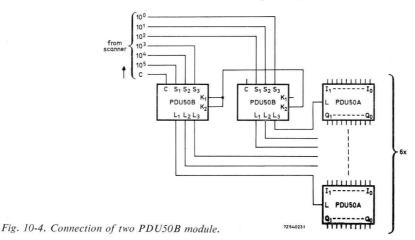

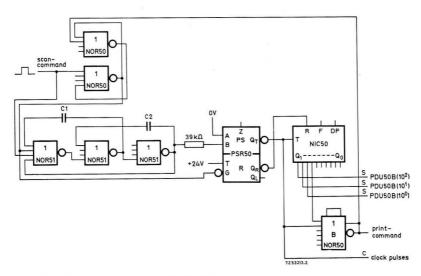

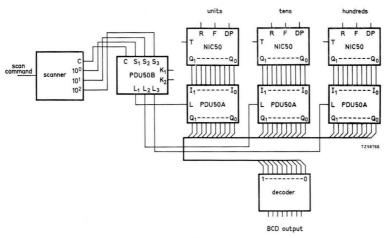

|       | 10.3         | The scanning circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57       |

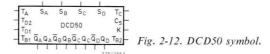

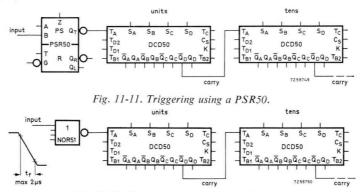

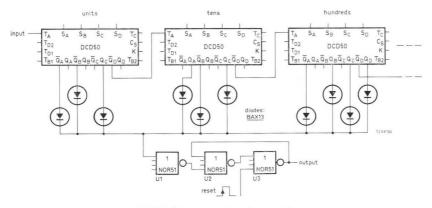

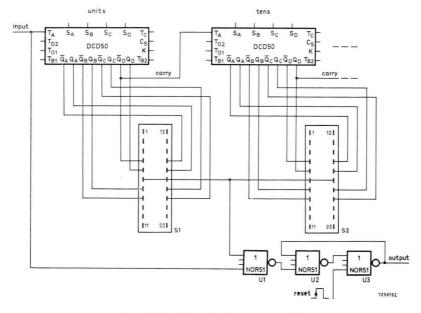

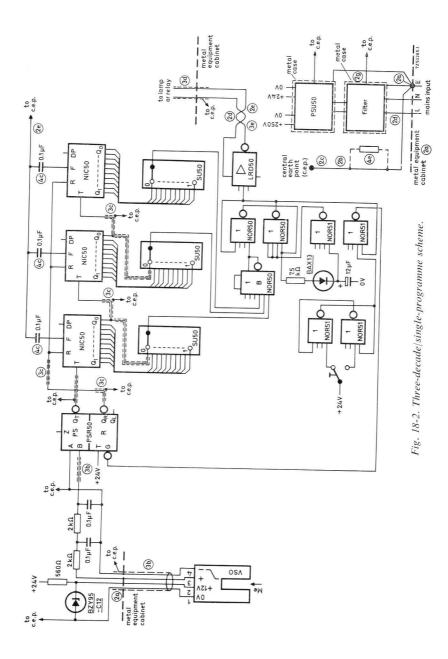

| 11    | Deca         | de and Divider Circuits with the DCD50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59       |

|       | 11.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59       |

|       | 11.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59       |

|       | 11.2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62       |

|       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63       |

|       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64       |