# PRODUCT DESCRIPTION µPD 78C06 µPD 78C06A

## NEC ELECTRONICS (EUROPE) GMBH

3

PRODUCT DESCRIPTION µPD 78C06 µPD 78C06A

8/84 V1.2

## Table of Contents

•

## Page

| GENER  | AL DESCRIPTION                                   | 1  |

|--------|--------------------------------------------------|----|

| FEATU  | RES                                              | 2  |

| PIN CO | ONFIGURATION                                     | 4  |

| 1.     | PIN DESCRIPTION                                  |    |

| 1.1    | PA <sub>7-0</sub> (PortA)Output                  | 7  |

| 1.2    | PB <sub>7-0</sub> (PortB)3-state Input/Output    | 7  |

| 1.3    | PC <sub>5-0</sub> (PortC)Input                   | 10 |

| 1.4    | WR (Write Strobe)Output                          | 10 |

| 1.5    | RD (Read Strobe)Output                           | 11 |

| 1.6    | TO (Timer Out)Output                             | 11 |

| 1.7    | DB <sub>7-0</sub> (Data Bus)3-state Input/Output | 11 |

| 1.8    | PE <sub>15-0</sub> (PortE)Output                 | 11 |

| 1.9    | WAIT (Wait Request)Input                         | 12 |

| 1.10   | INTO, INT1 (Interrupt Request)Input              | 12 |

| 1.11   | $x_1, x_2$ (Xtal)                                | 13 |

| 1.12   | $\phi$ out (Clock Output) Output ,               | 13 |

| 1.13   | SCK (Serial Clock)Input/Output                   | 14 |

| 1.14   | SI (Serial Input)Input                           | 15 |

| 1.15   | SO (Serial Output)Output                         | 15 |

| 1.16   | REL (Release STOP mode)Input                     | 15 |

| 1.17.  | RESET (Reset)Input                               | 15 |

| 2.     | INTERNAL BLOCK FUNCTIONS                         |    |

| 2.1    | Registers                                        | 17 |

| 2.2    | Arithmetic Logic Unit (ALU)                      | 18 |

| 2.3    | Memory                                           | 19 |

| 2.4    | Serial Interface                                 | 22 |

| 2.5    | Serial Mode Register (SM)                        | 25 |

|   | 2.6    | Timer                                          | 25 |

|---|--------|------------------------------------------------|----|

|   | 2.7    | Timer Mode Register (TMM)                      | 28 |

|   | 2.8    | Mode B                                         | 28 |

|   | 2.9    | Program Status Word (PSW)                      | 29 |

|   | 2.10   | Stand-by Control Register (SC)                 | 32 |

|   | 2.11   | Interrupt Control Block                        | 33 |

|   | 3.     | INTERRUPT OPERATION                            |    |

|   | 3.1    | Priority level                                 | 37 |

|   | 3.2    | Masking                                        | 38 |

|   | 3.3    | Sampling of External Interrupt                 | 38 |

|   | 4.     | INTERRUPT PROCEDURE                            | 41 |

|   | 5.     | STAND-BY OPERATION                             | 43 |

|   | б.     | RESET OPERATION                                | 46 |

|   | 7.     | CLOCK DRIVER CIRCUIT                           | 48 |

|   | 8.     | BUS TIMING                                     |    |

|   | 8.1    | OP Code fetch                                  | 49 |

|   | 8.2    | Memory read                                    | 50 |

|   | 8.3    | Memory write                                   | 51 |

|   | 9.     | STRING OF THREE 'SPECIAL' INSTRUCTIONS         | 52 |

| 1 | 0.     | uCOM-87LC INSTRUCTION-SET                      |    |

| 1 | 0.1    | Symbols/Descriptions on Operand                | 53 |

| 1 | 0.2    | Description of the Symboles on Operation Codes | 55 |

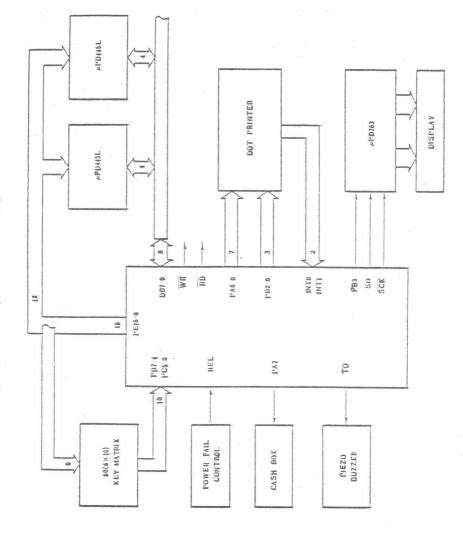

| 1 | 1.     | SYSTEM CONFIGURATION EXAMPLE                   | 63 |

| 2 | PPENDI | ХА                                             | 65 |

| 7 | PPENDI | Х В                                            | 66 |

| A | PPENDI | х с                                            | 67 |

#### uPD78C06/78C06A \*

## SINGLE-CHIP 8-BIT MICROCOMPUTER

| GENERAL<br>DESCRIPTION | The NEC uPD78C06/78C06A is a general purpose single-chip |

|------------------------|----------------------------------------------------------|

|                        | microcomputer. The uPD78C06/78C06A is fabricated with    |

|                        | CMOS technology                                          |

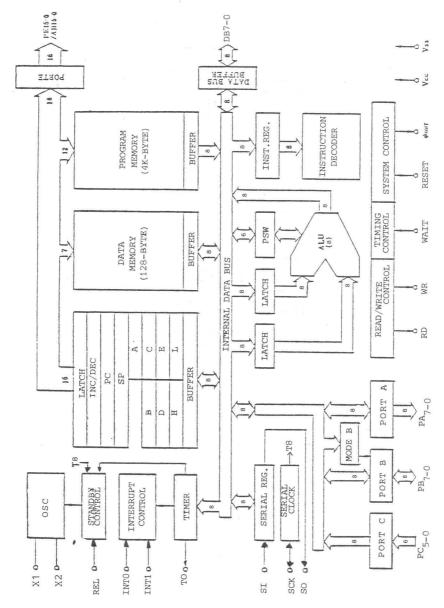

This contains the functional blocks of program memory, data memory, ALU, I/O ports, on-chip timer serial I/O, and internal clock generator. It can extend external memory capacity (ROM, RAM) up to 60K bytes.

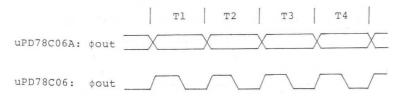

uPD78C06A is a high speed version of uPD78C06, but only  $\phi$  out function of uPD78C06A is different from uPD 78C06. uPD78C06As  $\phi$  out is 1/8 of crystal frequency, but uPD78C06s is 1/4 of crystal frequency.

Therefore, the uPD78C06A is 33% factor in instruction - execution than the uPD78C06.

As the uPD78C06/78C06A is a CMOS device and provided with the standby function, it is suitable for application of hand-held computers requiring low power consumption. It is also suitable for application in control field because of its rich input/output functions, timer function and bit operation function.

(NOTE)

\* 78C06/06A means not only 78C06/06A but also 78C05/05A (Evaluation chip) except the cases where specifically mentioned its difference.

FEATURES

Single-chip Microcomputer (uCOM-87LC)

powerful 101 Instructions

Transfer ..... 17

Operation .... 60

Rotation ..... 4

Jump ..... 4

Call/Return ... 6

Port output ... 2

Others ..... 8

Instruction Cycle Time : 6 us (on-chip ROM) (at 4MHz;uPD78C06)

4 us ( " )(at 6MHz;uPD78C06A)

4 us (external memory & on-chip RAM)

(at 4MHz;uPD78C06)

2.76 us ( " )(at 6MHz;uPD78C06A)

Program Memory (ROM) : 4096W x 8 Data Memory (RAM) : 128W x 8 Direct Addressing Capability up to 60kB External Memory Powerful Addressing Modes Capability

Register, register indirect, auto-increment, auto-

decrement, working register, immediate, direct, relative Multi-level Stack

Vectored Interrupts (External : 2, Internal : 1) On-chip 8-bit Timer with 4-bit Prescaler

46 I/O lines

8-bit output port (PA0-7)

8-bit input/output port (PB0-7)

8-bit input port (PC0-PC5)

8-bit data bus (DB0-7)

Serial I/O Ports

Stand-by Capability (STOP/HALT mode)

Fully Bus Compatible with 8080A

On-chip Clock Generator

Single Supply, CMOS Technology

Clock output (¢out):

uPD78C06 - fosc/4 ( = internal system clock)

uPD78C06A - fosc/8 ( = half of internal system clock)

Low Power Consumption

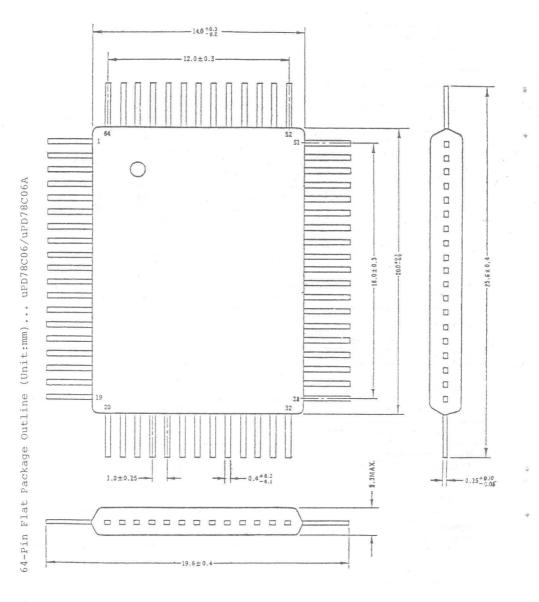

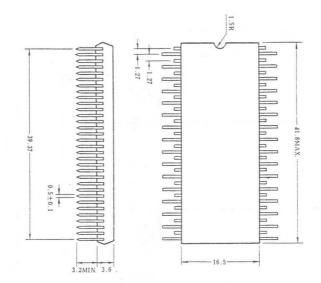

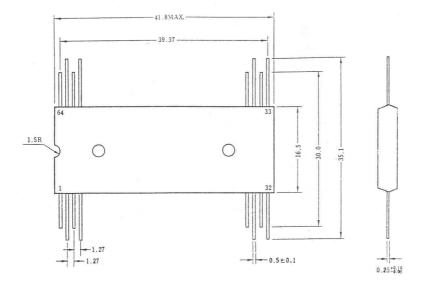

64 pin Plastic Flat Package (uPD78C06/uPD78C06A)

64 pin Plastic QUIP Package (uPD78C06A)

PIN CONFIGURATION

(TOP VIEW)

¥

104

Pin Names

PA7-0, PB7-0, PC5-0, PE15-0 : I/O Ports : Data Bus DB7-0 WAIT : Wait Request : Interrupt Request INTO, INT1 : Xtal X<sub>2</sub>, X<sub>1</sub> : Serial Clock Input/Output SCK : Serial Input SI : Serial Output SO RESET : Reset RD : Read Strobe WR : Write Strobe ¢ out : Clock Output

NC: Non-connection

uPD78C06/uPD78C06A Block Diagram

## 1. PIN DESCRIPTION

## 1.1 PA7-0 (PortA) ... Output

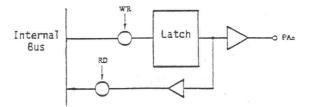

This is a 8-bit output port, and it has latch capability. With Move instructions, the data can be transferred between latch buffers and accumulator. Besides, the latched contents on the buffers can be freely handled with Logic instructions. Once the data is written on the buffers, it is kept on the buffers until another Port A handling instructions will be executed or a reset signal will be issued. Output level is TTL compatible.

When the RESET signal is entered, the latch contents are cleared and the low level signal is output.

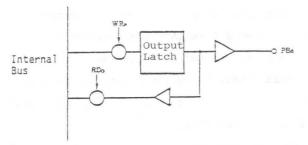

Fig. 1-1 The Port A Structure 1.2 PB<sub>7-0</sub> (PortB) ... 3-state Input/Output

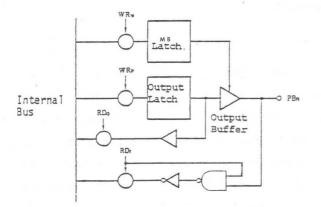

This is a 8-bit input/output port, and its output has latch capability. Each line of the Port B can be independently manipulated by the MODE B Register, and either of an input or output port can be programmed at that time. In case of being set as input port lines, or during reset, the port lines become a high impedance state. Input level is CMOS compatible and output level is TTL compatible.

The output latch contents are cleared (0) with the RESET signal.

Fig. 1-2a The Port B Structure

(a) A bit of the Port B is defined as an output port (MODE Bn=0) In this case, an output latch contents can be output from PBn. And with move instructions, the data can be transferred between output latch buffers of the port-lines and an accumulator.

(continued)

The latched contents can be freely handled with Logic instruction. Once the data is written on the output, the latch will maintains the data until another Port B handling instriction will be executed or a reset will be issued.

Fig. 1-2b The lines of the Port B used as output ports

(b) A bit of the Port B is defined as an input port (MODE · Bn=1) The content of the PB lines can be loaded onto the accumulator with a move instruction. Also a write operation into output latch of the port lines are possible, too, i.e., by a move instruction, the data on the accumulator can be stored into all the output latchs of the Port B, no matter whether a port line is set as input or output port. However, the contents of the output latch buffers of the port lines used as input port cannot be loaded onto the accumulator, by a move instruction. Besides, since the output latch buffers of the input ports are high impedance state, the contents of the buffers do not appear on the port lines. But, if the port lines then are switched over from input mode to output mode, the contents stored in the above mentioned output latchs can appear on the port lines, and can be loaded into the accumulator.

Fig. 1-2c The lines of the Port B used as input ports

(continued)

However, an actual instruction execution is done per 8-bit data. If a Port B read instruction (MOV A,PB) is executed, the contents of input lines set as input ports and the ones of output latches set as output ports are loaded into the accumulator. If a Port B write instruction (MOV PB,A, etc.) is executed, the contents of the output latch buffers set as input ports are replaced with another data by the instruction execution, but input lines are not affected by it.

```

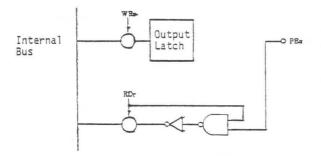

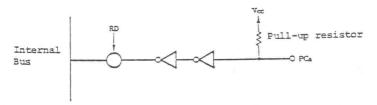

1.3 PC<sub>5-0</sub> (Port C) ... Input

```

This is a 6-bit input port with pull-up resistors. Input data to this port can be tested by test instruction, and also moved to least significant 6-bit of accumulator and higher 2 bit of accumulator are loaded with "0". Input level is CMOS compatible. This port is fit for key-input port.

Fig. 1-3 The Port C Structure

1.4 WR (Write Strobe) ... Output

This is used as a strobe signal for a write operation for an external memory or I/O. This is at the high level in inactive condition.

## 1.5 RD (Read Strobe) ... Output

This is used as a strobe signal for a read operation for an external memory or I/O. This is at the high level in inactive condition.

1.6 TO (Timer Out) ... Output

The square wave is output from this line. Its cycle time is half of a count time of the internal timer. It goes on low level after reset.

1.7 DB7-0 (Data Bus) ... 3-state Input/Output

This is an 8-bit bi-directional data bus. The data move between an external memory or I/O, and accumulator is done through this data bus. During an input, HALT, STOP mode and RESET, the output of the data bus goes an high impedance state. Input/Output level are TTL compatible.

1.8 PE15-0 (Port E) ... Output

This is a 16-bit address bus/output port. There are two ways to use these lines as follows: Output level is TTL compatible.

(a) 16-bit Output Port Mode (Only applicable to 78C06/06A)

If users do not want to extend any external memory on the system, they can use the full 16-bit lines of the Port E as general purpose output ports; by a PEX instruction, the contents of the B register and C Register appear on  $PE_{15-8}$  and  $PE_{7-0}$ , respectively. By an execution of a PEX instruction, this mode can be set, automatically. RESET signal also sets the port to this mode (different to  $\mu$ PD78C05/C05A). By RESET signal, the output latch buffers are cleared, and its output level goes to low.

(continued)

(b) 16-bit Address Bus Mode

If users want to attach external memories up to 60K bytes to the uCOM-87LC (uPD78C06), they can attain their intention by using all these lines as 16-bit address bus. This mode can be set by a PER instruction. In this mode, the data of the internal address bus are always placed on  $PE_{15-0}$  disregarding internal or external memory access. Address bus data are retained in halt-mode and are forced to low in stop-mode.

1.9 WAIT (Wait Request) ... Input If users use rather slow speed external memories or I/O devices in the systems, they can extend a READ/WRITE timing to meet this slow device, by providing a low level signal to this line. The WAIT signal is checked at the end of  $T_2$ . If it is low, it goes to a wait state (Tw), and it stays in the state until the WAIT goes high. Pull-up register is built-in.

1.10 INT0, INT1 (Interrupt Request) ... Input These are Interrupt Request Input lines. INT0 is a level-sensitive, INT1 is a rising-edge sensitive, respectively. The interrupt priority among the interrupts is shown below.

INT 0 > INT T > INT 1

Here, INTT is internal interrupt.

(a) INT 0

It is a level-sensitive interrupt input line which is high level active.

#### (b) INT 1

It is a rising-edge sensitive interrupt line, and it becomes valid when INT 1 input goes low to high. Subsequently, if users want to perform the next INT 1 interrupt on this line after an interrupt on this line is accepted, they must take it into consideration that INT 1 input should be maintained at low state a little while, and then it should go high. Unless, it does not enable the next INT 1 interrupt.

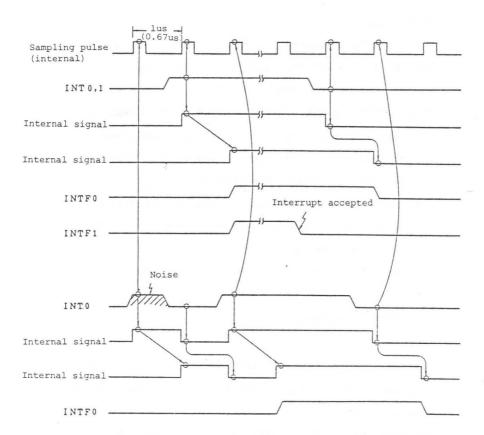

In order to avoid a possible mis-operation due to noise signals, both of two interrupt lines are sampled with internal clocks of lus cycle (at 4MHz operation) or 0.67us (at 6MHz operation) in the uPD78C06 or uPD78C06A so that noise signals less than lus and 0.67us are not accepted. Therefore, an interrupt request signal must have an active (high level) time of more than 2us and 1.33us in the uPD78C06 and uPD78C06A, respectively with respect to both INT 0 and INT 1.

## 1.11 X1, X2 (Xtal)

These are connected to the crystal for the internal clock generator circuit. The  $X_1$  is also used as the external clock input, instead of the crystal. Input level of  $X_1$  is CMOS compatible. System clock is a quarter of the crystal frequency or external clock frequency.

1.12  $\phi$  out (Clock Output) ... Output

In the uPD78C06, uPD78C05 and uPD78C05A 1/4 of crystal oscillation frequency or external clock frequency is output, that is,

a clock of 1MHz at 4MHz operation.

In the uPD78C06A, a clock of 1/2 of the system clock frequency (1/8 of crystal oscillation frequency or xl external clock frequency), that is, a clock of 750kHz at 6MHz operation is output. The clock output (\$\phi\$out) continues in the hold mode, but it is fixed to the high level in the stop mode. The clock output (\$\phi\$out) can be optionally used for synchronization with an external device and other purposes. In the uPD78C06A, since the clock output (\$\phi\$out) frequency is 1/2 of the system clock frequency, high and low levels are not determined for each basic clock cycle (T1 - T4).

1.13 SCK (Serial Clock) ... Input/Output

This is used as control clocks for serial input/output data. The serial clock generated in the internal circuit is placed out in internal serial clock mode, and the external clock is input to this line in external serial clock mode. At the rising edge of  $\overline{SCK}$ , the data on a SI line is loaded to the Serial Register (S/P), and at the falling edge of  $\overline{SCK}$ , the contents of the Serial Register appear on a SO line with a bit-order from MSB to LSB. Internal serial clock frequency is a half of system clock frequency (fosc/8).

1.14 SI (Serial Input) ... Input

This is a serial output port, and the data on the SI is loaded to the Serial Register at the rising edge of  $\overline{SCK}$ . The MSB is start bit.

1.15 SO (Serial Output) ... Output

This is a serial output port, and the data on the Serial Register appears on the SO. The MSB is start bit.

1.16 REL (Release STOP mode) ... Input

This is an input to release the STOP mode of stand-by function. STOP mode is released by raising the REL input high, then clock generator which has been stopped will restart. During REL input is high, the bit 3 of Stand-by Control Register (SC3) is set to one, and it is reset to zero after REL signal returns low. Pull-down resistor is built in.

1.17 RESET (Reset) ... Input

When a low level signal over 8us (at 4MHz operation) and 5.34us (at 6MHz operation) is entered in the uPD78C06 and uPD78C06A, respectively, the system is reset and the uPD78C06/uPD78C06A goes to the following conditions;

- All interrupt mask register bits are set, and the all interrupt sources are masked.

- An interrupt enable flag is reset, and all interrupts are disabled.

- All interrupt request flags are reset, accordingly all pending interrupts are reset, too.

- MODE B register is set to FFH, and the Port B lines become an input mode.

- The bit 6 of Serial Mode Register (SM6) is set, and the serial clock is in external mode.

- The bit 3 of Stand-by Control Register (SC3) is reset, other bits are set. Both the HALT and STOP mode are released.

PSW are all reset to zero.

- ° PC is loaded with 0000H.

- ° The Prescaler and Upcounter in timer circuits are cleared.

- ° All TIMER.REG bits are set to FFH.

- All Timer Mode Register (TTM) bits are set. As a result,

TO goes to low and the timer circuit becomes the mode of adding PRESCALER 0.

- ° All Port A outputs go to low.

- ° Port E becomes port mode, and its output level becomes low.

- ° Data bus (DB7.DB0) goes to high impedance.

- ° SO output goes to low.

- ° WR, RD output go to low.

- Other internal registers and RAM, etc. in CPU are not specified.

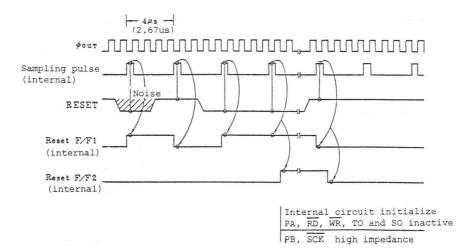

In order to avoid a possible mis-operation due to noise signals, this line does not accept level changes less than 4us and 2.67us by sampling at every 4us (at 4MHz operation) in the uPD78C06 and 2.67us in the uPD78C06A, respectively. Accordingly, a low level over 8us and 5.34us are required in the uPD78C06 and uPD78C06A, respectively to accept RESET asynchronously and exactly. Following RESET goes to high, program starts from location 0000H.

2. INTERNAL BLOCK FUNCTIONS

## 2.1 Registers

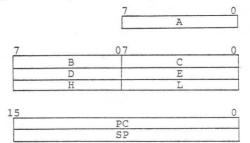

This mainly consists of the seven 8-bit registers and two 16-bit registers as below.

Fig. 2-1 Register Configuration

(a) General Purpose Registers (B, C, D, E, H, L)

In addition to a role of auxiliary registers for the accumulator, these registers also have a Data Pointer capability if they are used as pair-register (BC, DE, HL). There is an auto-increment/decrement addressing mode capability for the pair-registers of DE, HL, and it can contribute to increase the program efficiency.

(c) Accumulator (A)

Since the uPD78C06/06A has an accumulator based architecture, all the data operation are done through the accumulator.

## (d) Program Counter (PC)

This is a 16-bit register to maintain the address information of a program step which should be executed, next. According to a number of bytes needed for an instruction which is going to be fetched, it is automatically incremented, usually. However, in case of executing a branch instruction, an immediate data or content of a register appears on the PC. If a reset signal is issued, or in stop mode the PC is reset to 0000H.

(e) Stack Pointer (SP)

The Stack Pointer is a 16-bit register and is used to maintain a top of the address information of the stack area (Last-In-First-Out Style). The content of the SP is decremented if a CALL or PUSH instruction is executed or interrupt happens, and it is incremented if an RETURN or POP instruction is executed.

## 2.2 Arithmetic Logic Unit (ALU)

This is used to perform a arithmetic and logic operation such as binary addition/subtraction, decimal adjust, logic and compare operation, and rotation or digit-rotation etc.

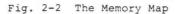

2.3 Memory

The uPD78C06/78C06A can directly address the memory up to 64k bytes. Except on-chip ROM (0-4095) and RAM (65,408-65535), any memory location can be used as cither of RAM or ROM, freely. The memory map of the uPD78C06/78C06A is shown on the next page. In the internal ROM area, the Reset/Stop mode Restart Address, Interrupt Start Address, Call Table etc. are included. External memory and on-chip RAM area can be used as data memory (RAM), program memory (ROM), and/or working registers, freely.

(a) Interrupt Start Address

| Interrupt<br>Source | Starting<br>Address |

|---------------------|---------------------|

| INTO                | 4 (0004H)           |

| INTT                | 8 (0008H)           |

| INT1                | 16(0010H)           |

Since each interval among interrupt addresses is not the same, it is necessary to put an adequate interrupt service program for pre-treatment of data to interrupts.

(b) Call Address Table

This is used to store the call-address of each one-byte Call instruction over location 128-225 (CALT); up to 64 call-addresses. (c) Internal Program Memory Area (On-Chip ROM) (Only applicable to 78C06/06A)

There is on-chip 4k bytes ROM area over location 0-4095 on the memory space. When users write the program onto the internal ROM area, they should take care of the built-in Reset Address, Interrupt Start Address and Call-Table on the ROM area. Users can directly address the memory area over location 2048-4095 with 2-byte Call instruction (CALF).

- (d) Internal Data Memory Area (On-Chip RAM)There is on-chip 128 bytes RAM area over location 65408-65535.

- (e) External Extended Memory Area

Users can extend data and/or program memory area by using address bus  $(PE_{15-0})$ , data bus  $(DB_{7-0})$ , and RD, WR Signals up to external 60k bytes memory area (4096-65407).

$\overline{\text{RD}}/\overline{\text{WR}}$  signals are not output in program area 0-4096 and RAM-area 65408-65535.

(f) Working Register Area

On the location 65280 to 65535, the working registers which contain the 256 bytes area can be located.

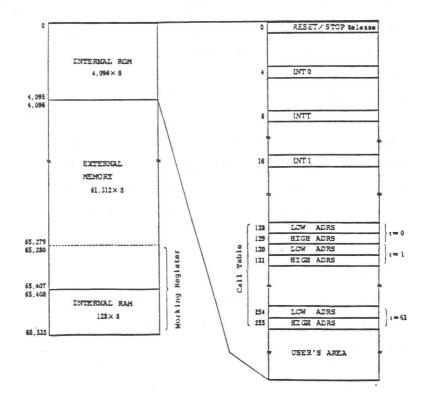

## 2.4 Serial Interface

Serial interface section (see Fig. 2-3) consists of Serial Input (SI) line, Serial Output (SO) line, Serial Clock ( $\overline{SCK}$ ) input/output line, an 8-bit Serial Register (S/P), an octal counter, a R-S flip-flop used for transfer control, and some gates. The serial clock becomes the internal clock mode fixed to the frequency of 1/2 of the system clock (500kHz at 4MHz operation in the PD78C06 and 750kHz at 6MHz operation in the PD78C06A, respectively) when the bit 6 (SM6) of the serial mode register is set to  $\emptyset$ . On the other hand, when SM6 is 1, the external clock mode is set and external clocks of DC - 500kHz and DC - 750kHz are entered in the uPD78C06 and uPD78C06A, respectively. Accordingly, the transfer operation in internal clock mode performed synchronously with constant frequency, and in external clock mode it is performed synchronously with variable

A transmitting data is set to serial register by MOV S, A instruction, then the octal counter is reset and serial transfer is triggered by SIO instruction. At every falling edge of  $\overline{SCK}$ , the contents of serial register are shifted, and shift-out data are placed to SO line with starting bit of MSB. While the  $\overline{SCK}$  is low the data on SI line is loaded in continuously, and then latched to serial register at the rising edge of the  $\overline{SCK}$ . Like this both the input and output of serial data are performed by same  $\overline{SCK}$ .

Fig.2-3 The Block Diagram of Serial Ports

After occuring eight SCK pulses and completing 8-bit serial data transfer the carry T8 is generated from the octal counter and it sets the interrupt request flag (INTFS). But uPD78C06/78C06A has no serial interrupt, then INTFS is checked by test instruction (SKNIT FS). In internal SCK mode, as T8 signal resets the control flip-flop, the following transfer is disabled until next SIO instruction will be given.

Accordingly, the data transfer should be restarted by SIO instruction with the next conditions. In case of data reception, after receiving the data from serial register by MOV A,S instruction, and in case of data transmission, after setting the data to serial register by MOV S,A instruction, data transfer must be done by new SIO instruction.

T8 is also generated in case of external  $\overline{SCK}$  mode, however, it has no effect to control the external  $\overline{SCK}$ , so that it is necessary to control the number of  $\overline{SCK}$  by the external  $\overline{SCK}$  source side.

In case of external  $\overline{SCK}$  mode, the trigger by SIO instruction are not required basically, but to avoid a mis-operation by noise on  $\overline{SCK}$  line, the data transfer should be restarted by SIO instruction which resets the octal counter, after setting or receiving the data to /from serial register as in internal  $\overline{SCK}$ , after completing 8-bit transfer.

RESET input cause the SO to low level and the  $\overline{SCK}$  is set to external clock mode.

2.5 Serial Mode Register (SM)

This is an 1-bit register used to specify the serial clock source (internal or external) as the SCK, SM is set to 1 by RESET input, then the external clock is selected as serial clock source, and cleared to 0 by move instruction (MOV SM,A ; A=X0XXXXXX), then the internal clock is selected. SM (SM6) is referenced to bit 6 of accumulator. See following format.

Fig. 2-4 Serial Mode Register Format

| 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |   |                |

|---|-----|---|---|---|---|---|---|---|----------------|

| - | SM6 | - | - | - | - | - | - |   |                |

|   |     |   |   |   |   |   |   | 0 | Internal Clock |

|   |     |   |   |   |   |   |   | 1 | External Clock |

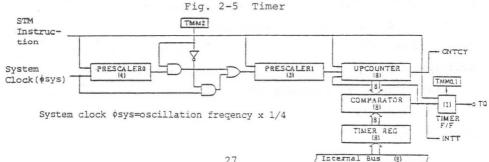

2.6 Timer

This is an programmable 8-bit interval timer with prescaler. It consists of TIMER REG (8-bit), PRESCALERO (4-bit), PRESCALERI (3-bit), UPCOUNTER (8-bit), COMPARATOR (8-bit), and TIMER F/F.

Count time and TO output are controlled by Timer Mode Register (TMM). Resolution and count time shown in the following table can be selected according to the count data set in the bit 2 (TMM2) of the timer mode register and TIMER.REG.

| Set value of       | TMM      | 2 = 0     | TMM2 = 1 |                            |  |

|--------------------|----------|-----------|----------|----------------------------|--|

| TIMER·REG<br>(HEX) | uPD78C06 | uPD78C06A | uPD78C06 | uPD78C06A<br>85.3<br>170.6 |  |

| 00                 | 8        | 5.33      | 128      |                            |  |

| 01                 | 16       | 10.66     | 256      |                            |  |

| 02                 | 24       | 15.99     | 384      | 255.9                      |  |

| 03                 | 32       | 21.32     | 512      | 341.2                      |  |

| Î                  |          | ~ ~       |          | );                         |  |

| FD                 | 2,032    | 1353.82   | 32,384   | 21,666.2                   |  |

| FE                 | 2,040    | 1359.15   | 32,640   | 21,751.5                   |  |

| FF                 | 2,048    | 1364.48   | 32,768   | 21,836.8                   |  |

Count time (us)

Note: It is assumed that the uPD78C06 is operated at 4MHz and the uPD78C06A is operated at 6MHz, respectively.

At first set the count value to the TIMER REG by MOV TM, A instruction, then initialize the PRESCALERO, 1, TIMER F/F, UPCOUNTER and start timer by STM instruction.

UPCOUNTER is counted up at every 8us (TMM2 = 0) or 128us (TMM2 = 1) in the uPD78C06 (at 4MHz operation) and 5.33us (TMM2 = 0) or 85.3us (TMM2 = 1) in the uPD78C06A (at 6MHZ operation).

COMPARATOR always compares the contents of UPCOUNTER with TIMER REG, and it generates match signal (internal interrupt ; INTT) when they are matched. The match signal clears the content of UPCOUNTER, and restarts the countup. Accordingly, this timer operates as the interval timer which generates repetitive interrupt with the interval of count time specified by count value of TIMER REG. When a timer interrupt is generated in HALT mode, the HALT mode is released. Note that the timer interrupt is disabled by setting the bit 1 of interrupt mask register (MK1) to 1. The content of TIMER F/F whose state is changed by every match signal from COMPARATOR is placed on the TO line, so that the TO signal

becomes the square wave with its half cycle time equivalent to count time.

This output is suitable for driving a piezo buzzer, etc. When the set value of TIMER REG is assumed to be 00H, a coincidence signal (internal interrupt: INTT) is generated after the first set time elapses and the contents of UPCOUNTER are cleared and the TO output is changed from low to high level. However, unlike the case of the set value other than 00H, the count operation is not repeated thereafter, the coincidence signal (internal interrupt: INTT) is not generated and UPCOUNTER is not cleared. This state continues until any one of the following conditions takes place. (TO output is held high.)

1 RESET input becomes low level.

2 STOP mode is set.

3 STM (Start Timer) instruction is executed.

Therefore, it should be noted that when 00H is set, the timer does not work as an interval timer.

After RESET input or STOP mode is set, the operation is the same as the normal operation.

If STM instruction is executed to go out of this state without changing the set value of TIMER.REG (00H is held), the TO output returns to low level immediately after execution of the STM instruction and it is held again at high level after the set time is over.

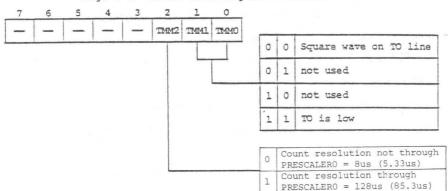

## 2.7 Timer Mode Register (TMM)

This is a 3-bit register used to control the timer operation. Its contents are transferred to/from the accumulator by move instruction. It is referenced to bit 0-2 of accumulator.

Bit 0 and 1 of timer mode register (TMM0,1) enable or disable the square wave output of TO, and bit 2 (TMM2) controls the PRESCALERO.

Fig. 2-6 Timer Mode Register Format

The figures in ( ) indicate the values in the case of uPD78C06A.

#### 2.8 MODE .B

This is an 8-bit Register used for programming the input/output modes of the Port B. With Move instructions (MOV MB, A), programmer can determine the contents of the MODE.B freely. They can program each bit line as either of input or output mode, individually.

If one of the bits of MODE B register is set to one, then corresponding bit of PB line becomes input, and if it is reset to zero, then corresponding bit of PB line becomes output. All MODE B register bits are set to one by RESET input.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |   |                  |

|-----|-----|-----|-----|-----|-----|-----|-----|---|------------------|

| MB7 | MB6 | MB5 | MB4 | MB3 | MB2 | MB1 | MBO |   |                  |

| 1   | - 1 | 1   | 1   | 1   | 1   |     | .   |   |                  |

|     | -   |     |     |     |     |     |     | 0 | PBn= Output Mode |

|     |     |     |     |     |     |     |     | 1 | PBn= Input Mode  |

|     |     |     |     |     |     |     |     |   | n=0-7            |

## Fig. 2-7 Mode B Register Format

2.9 Program Status Word (PSW)

It contains the six flags which are set or reset by the results of instruction execution. Two of these flags (Z, CY) can be tested with instructions. The contents of the PSW are automatically saved onto the Stack at interrupt occurrence (External Interrupt, Internal Interrupt), and are retrieved by RETI instruction. All the contents are reset to 0 by the RESET input or STOP mode.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |     |

|----|----|----|----|----|----|----|----|-----|

|    | Z  | SK | HC | Ll | LO |    | CY | PSW |

#### Fig. 2-8 PSW Format

(a) Z (Zero)

If an result of execution is 0, it is set to 1, otherwise it is reset to 0. By instruction, it can be tested.

(b) SK (Skip)

If the Skip condition is just complete, it is set to 1, otherwise it is reset to 0.

(c) HC (Half Carry)

If a Carry from the Bit 3 of the accumulator occurs as a result of operation, it is set to 1, otherwise it is reset to 0.

(d) L1

If a string of MVI A, byte instructions is executed, it is set to 1, otherwise it is reset to 0.

(e) L0

If string of MVI L, byte or LXI H, word instructions is executed, it is set to 1, otherwise it is reset to 0.

(f) CY (Carry)

If a Carry from the Bit 7 of the ALU occurs as a operation result, it is set to 1, otherwise it is reset to 0. By instructions, it can be tested.

(g) The Correlation of flags with instruction executions By execution of 18 kinds of ALU instruction, rotation instructions and Carry manipulation instructions, the flags of the uPD78C06/78C06A are affected as shown in the following table.

## Table 2-1 Flag Operation

|         | Oper   | ation   |                                                                                                                  |       | 06 | D5 | D4 | D3 | D2 | D0 |  |

|---------|--------|---------|------------------------------------------------------------------------------------------------------------------|-------|----|----|----|----|----|----|--|

| reg.    | memory | im      | mediata                                                                                                          | skip  | Z  | SK | HC | LI | ы  | CY |  |

| DD      | ADDX   | ADI     |                                                                                                                  |       |    |    |    |    |    |    |  |

| DC      | ADCK   | ACI     |                                                                                                                  |       |    | 0  | :  | 0  | 0  |    |  |

| SUB     | SUBX   | sui     |                                                                                                                  |       |    |    | -  | 0  |    | •  |  |

| 588     | SBBX   | SBI     |                                                                                                                  |       |    |    |    |    |    |    |  |

| ANA     | ANAX   | ANI     | ANTW                                                                                                             |       |    |    |    |    |    |    |  |

| ORA     | ORAX   | ORI     | ORIW                                                                                                             |       | :  | 0  |    | 0  | 0  |    |  |

| CRA     | XRAX   | XRI     |                                                                                                                  |       | 1  |    |    |    |    |    |  |

| ADDNC   | ADDNCK | ADINC   |                                                                                                                  |       |    |    |    |    |    |    |  |

| SUENB   | SUBNBX | SUINB   |                                                                                                                  |       | :  |    |    |    | 0  | Ι. |  |

| TA      | GTAX   | GTT     | GTTW                                                                                                             |       |    | -  | •  | 0  | 0  | •  |  |

| LTA     | LTAX   | LTT     | LTIW                                                                                                             |       | 1  |    |    |    |    |    |  |

|         | ONAX   | ONI     | ONTW                                                                                                             |       | 1. |    |    | Γ. |    |    |  |

|         | OFFAX  | OFFI    | OFFTW                                                                                                            |       | 1: | :  |    | 0  | 0  |    |  |

| NEA     | NEAX   | NEL     | NEW                                                                                                              |       | 1. |    | :  | 0  | 0  |    |  |

| EQA     | EQAX   | EQI     | ECIW                                                                                                             |       |    |    |    |    | 0  | •  |  |

| INR     | INRW   | T       |                                                                                                                  |       | :  | :  |    | 0  | 0  |    |  |

| DCR     | DCRW   | 1       |                                                                                                                  |       | 1  | •  |    | Ľ  | -  |    |  |

| DAA     |        |         |                                                                                                                  |       | :  | 0  | :  | 0  | 0  |    |  |

| RLL,    | RLR    |         |                                                                                                                  |       |    | 0  |    | 0  | 0  | :  |  |

| RLD. RE | D      |         |                                                                                                                  |       |    | Ò  | •  | 0  | 0  |    |  |

| STC     |        |         |                                                                                                                  |       |    | 0  |    | 0  | 0  | 1  |  |

| CLC     |        |         |                                                                                                                  |       |    | 0  |    | 0  | 0  | 0  |  |

|         |        | MVI J   | byte                                                                                                             |       |    | 0  |    | 1  | 0  |    |  |

|         |        |         | -byte<br>word                                                                                                    |       |    | 0  |    | 0  | ı  | •  |  |

|         |        |         | and the second | SKINC | 1  | 1  | 1  | T  | T  | T  |  |

|         |        |         |                                                                                                                  | SKINZ |    | 1: |    | 0  | 0  |    |  |

|         |        |         |                                                                                                                  | SKNIT |    |    |    |    |    |    |  |

|         |        |         |                                                                                                                  | RETS  |    | 1  |    | 0  | 0  |    |  |

|         | All ot | her ins | truction                                                                                                         | s     |    | 0  |    | 10 | 0  |    |  |

Flag Affected (Set or Reset) Flag Set Flag Reset Flag Roset

2.10 Stand-by Control Register (SC)

The is a 5-bit register used to control the stand-by function, i.e. STOP or HALT mode. Bit 0-2,4 of Stand-by Control Register (SC0-2,4) can be set or reset by loading it with the contents of accumulator with MOV SC, A instruction. Bit 1 and 3 (SC1,3) can be moved to the corresponding bits accumulator with MOV A, SC instruction, and other bits of accumulator (A0, A2, A4-7) will be undefined.

RESET resets SC3, and sets other bits (SC0-2,4).

| 7 6   | 5 | 4   | 3   | 2  | 1               | 0   |                                                                                                               |

|-------|---|-----|-----|----|-----------------|-----|---------------------------------------------------------------------------------------------------------------|

| -   - | - | SCA | SCI | sœ | SCI             | SCO |                                                                                                               |

|       |   |     |     |    |                 |     | 0 STOP mode                                                                                                   |

|       |   |     |     |    |                 |     | 1 CPU operation mode                                                                                          |

|       |   |     |     |    |                 |     | Used for any software<br>flag,e.g.last flag used<br>to judge return from<br>STOP mode or restart by<br>RESET. |

|       |   |     |     |    |                 |     | O Release STOP mode by<br>carry from the coun-<br>ter in timer                                                |

|       |   |     |     |    |                 |     | 1 Release STOP.mode by<br>falling edge of REL<br>input                                                        |

|       |   |     |     |    |                 |     | 0 REL input=0 (low)<br>1 REL input=1 (high)                                                                   |

|       |   |     |     |    | tere an teresta | -   | 0 Set HALT mode<br>1 CPU operation mode                                                                       |

Fig. 2-9 Stand-by Control Register Format

Note that SC3 is not a control bit, but status bit to reflect a state of REL input directly. Accordingly, it will be possible to check the off-chattering of STOP mode release key signals, etc. by checking the content of SC3.

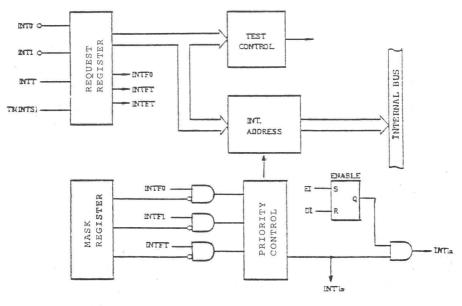

## 2.11 Interrupt Control Block

There are two external interrupts and one internal interrupt shown at the following, and all these are vectored interrupts.

|          | Interrupt Source                  | Starting<br>Address | Pri-<br>ority |

|----------|-----------------------------------|---------------------|---------------|

| External | INT 0 (Level)                     | 4                   | 1             |

| External | INT 1 (Rising Edge)               | 16                  | 3             |

| Internal | INT T (Match on timer comparator) | 8                   | 2             |

The interrupt Control Block contains INTERRUPT REQUEST Register, MASK Register, PRIORITY CONTROL, TEST CONTROL, INTERRUPT ENABLE F/F etc.

Fig. 2-10 Interrupt Control Block

#### (a) INTERRUPT REQUEST Register

It contains 3 kinds of interrupt request flags which are set to 1 by each interrupt, individually. By a system reset or STOP mode, all the flags are reset.

\* INTFO

This is a flag set by an external level interrupt (INTO). If the line receives a high level signal, this flag is set to 1. If it receives a low level signal, the flag is reset.

· INTF1

By the rising edge of an input signal to the INT1, the flag is set to 1.

· INTFT

This flag is set to 1 by match signal from the comparator in Timer.

\* INTFS

If a Serial Register completes the reception of 8-bit data through a SI line or if it completes the transmission of the data through a SO line, the flag is set to 1. However no interrupt is driven by this, and INTFS is checked by on SKNIT instruction.

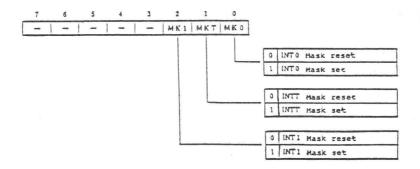

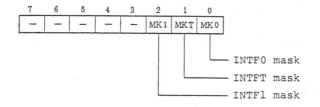

(b) MASK Register

It contains 3 bits mask flags corresponding to each interrupt. By instructions, each flag can be set or reset, freely. If a MASK bit is 1, the corresponding bit is masked.

Fig. 2-11 Mask Register Format

(c) PRIORITY CONTROL Circuit

This is the circuit used for controlling the interrupt priority among the interrupts mentioned in the above. If more than two interrupts occur in the system at the same timing, the uPD78C06/uPD78C06A accepts an interrupt which has a higher (or highest) priority than others.

INT 0 > INT T > INT 1

(d) TEST CONTROL Circuit

This circuit operates if instructions are executed which check a status of interrupt request flags (INTFO, INTF1, INTFT) or a test flag showing serial tranfer completion (INTFS).

## (e) INTERRÜPT ENABLE F/F

It is set by EI instruction, and is reset by DI instruction. Once any one of interrupts is accepted, it is reset. If this F/F is set to 1, it means 'Interrupt Enable'. If it is reset to 0, it means 'Interrupt Disable'. By a RESET input or STOP mode, it is also reset.

#### 3. INTERRUPT OPERATION

There are two external interrupts (INTO and INTL) and one internal interrupt (INTT). All of them are vectored interrupts and interrupt addresses are as shown below. In the data concerning interrupt signal sampling time used in the following description, the figures put in ( ) indicate the values at 6MHz operation of uPD78C06A and those not put in ( ) the values at 4MHz operation of uPD78C06.

| Tn       | terrun | t source                        | Interry | upt address |

|----------|--------|---------------------------------|---------|-------------|

| ± * *    | cerrap | 500100                          | Decimal | Hexadecimal |

| External | INT0   | Detection of<br>high level      | 4       | 0004        |

|          | INTL   | Detection of leading edge       | 16      | 0010        |

| Internal | INTT   | Coincidence of timer comparator | 8       | 0008        |

#### 3.1 Priority level

When several interrupt requests not masked by the mask register occur at a time in EI state, Several interrupt request flags (INTFx) are set. In such cases, the internal priority level control circuit selects the one of highest priority among those shown below and accepts that request only and reserves the others.

INTO > INTT > INT1

The flag of the accepted interrupt request is reset, but those of the others remain in being set until these interrupt requests are accepted.

3.2 Masking

All interrupt requests are masked (disabled) by DI instruction (resetting interrupt enable F/F) and permitted by EI instruction (setting interrupt enable F/F).

Even in EI state, masking is possible for each interrupt according to the mask register contents. When the corresponding bit of the mask register is set (1), that interrupt is masked and it is permitted by resetting the bit (0).

Fig. 3-1 Mask Register Function

The mask function is given strictly to the interrupt request flag (INTFx) which has been set by being recognized as a normal interrupt. Whether an external interrupt is permitted depends upon the external interrupt detect circuit having a sampling pulse of lus (0.67us) cycle.

3.3 Sampling of External Interrupt

Either INTO or INTI is detected in either active or inactive level by a sampling pulse of lus cycle (0.67us)

in order to prevent a malfunction due to a noise signal. (See Fig. 3-2.)

(1) INTO input

This is a level interrupt input of high level active. When high level of INTO signal with the sampling pulse of lus (0.67us) or more is detected, INTO request flag (INTFO) is set after one pulse. INTFO remains in being set as long as INTO signal is high level. When the sampling pulse detects low level of INTO signal, INTFO is reset after one pulse. Therefore, as INTFO remains in being set as long as INTO signal is high level even after interrupt service routine takes place and INTO signal is high level, reset INTO signal by informing the INTO signal source that the signal has been accepted by using the output port in the interrupt processing routine.

(2) INTl input

This is an edge interrupt input of leading edge active. When INTl signal changes from low to high level and the sampling pulse detects that high level of lus (0.67us) is being held, INTl request flag (INTFl) is set. When it is confirmed at the end of instruction that INTFl is being set, and if no other interrupt request flag with higher priority level is set, it jumps to the interrupt address corresponding to INTl interrupt request. When an interrupt is accepted, INTFl is automatically reset. A new INTl interrupt request is detected when INTl signal goes once to low and then high level, and INTFl is set.

Fig. 3-2 Sampling of Interrupt

As seen from the above description, as INTO and INTI are sampled by a clock of lus (0.67us) cycle, a noise signal of less than lus (0.67us) is eliminated. An interrupt is completely accepted with a high level input of 2us (1.33us) or more. 4. Interrupt Procedure

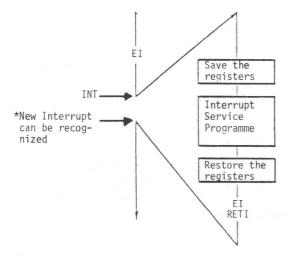

Each interrupt request is processed by the following procedure.

- Interrupt request flags are checked at T1 timing of first machine cycle of every instruction, and when it is set interrupt sequence will start. However the masked interrupt requests are not checked.

- If more than two interrupts are set at same time, then their priorities will be checked and the highest priority interrupt request is acknowledged, and others are pended.

(INT 0 > INT T > INT 1)

- Reset interrupt enable flip-flop, then all interrupts are disabled.

- Reset the interrupt request flag which is acknowledged, except for level-activated interrupt (INTO).

- Save the PSW, upper byte of PC, lower byte of PC onto the stack in this sequence.

For the whole interrupt procedure (without sampling-test for external interrupts) the uPD78C06/78C06A requires 4 internal clock cycles  $(4\mu \ sec/2, 68\mu \ sec)$ ; of course the processor has to finish the actual instruction before going to interrupt subroutine.

6) Jump to each interrupt starting address.

After execution of interrupt service program, it should be performed to return to the address where the interrupt was acknowledged. First, the programme restores registers or flags and interrupt enable flag is set by EI instruction. Then the lower byte of PC, the upper byte of PC and PSW are restored in this sequence by RETI instruction. To avoid a stack overflow another interrupt will be accepted after one instruction has been executed subsequent to EI instruction. This means a new interrupt can be recognized after completing an execution of RETI instruction following EI instruction and, as a result, the stack is restored completely.

\*: If an interrupt is acknowledged at location N, programme returns to location N after completing interrupt procedure.

Fig. 4-1 Interrupt Sequence

## 5. Stand-by operation

Stand-by function is used to decrease the power consumption in stand-by condition, and there are two types of it, HALT mode and STOP mode. It is specified to HALT mode by resetting the bit 4 of Stand-by Control Register (SC4), or STOP mode by resetting the bit 0 (SCO). HALT mode can be released by one of the external interrupt (INTO, 1), timer interrupt (INTT), carry form the serial clock counter (T8), and RESET signal. When HALT mode is released by an interrupt, program jumps to corresponding interrupt starting address in EI condition, or steps to the instruction following the HALT mode setting instruction (MOV SC,A) in DI condition. Yet in HALT mode the masking function is active, so that programmer can choose an interrupt source for release use. When HALT mode is released by T8, it returns the program control to an instruction of the main routine which is placed immediately after the instruction activating the HALT mode.

When HALT mode is released by  $\overline{\text{RESET}}$ , normal reset operation will be performed and program jumps to location 0. STOP mode can be released by REL or  $\overline{\text{RESET}}$  signal, and there are two ways of releasing (shown following) by REL signal according to the content of bit 2 of Stand-by Control Register (SC2).

### 1) In case of SC2=0

Start the oscillator and timer by rising edge of REL signal, and start to provide the internal clock after four carries (i.e. after 1,024 counts) from UPCOUNTER in timer, then program will start at location 0.

2) In case of SC2=1

Start the oscillator by rising edge of REL signal and inhibit to provide the internal clock during REL signal raised to high, and restart to provide the internal clock after REL signal returns to low, then program will start at location 0.

When STOP mode is released by RESET, normal reset operation will be performed, so that the oscillator will start at the falling edge of RESET, and program will start at location 0 by next rising edge. Accordingly, RESET should be held at low level sufficient time for oscillator to become stable.

## Table 5-1 HALT Mode and STOP Mode

| Parameter                               | HALT mode | STCP mode |

|-----------------------------------------|-----------|-----------|

| Oscillator                              | Run       | Stop      |

| Internal System Clock                   | Stop      | J.Cop     |

| Timer                                   | Run       |           |

| TIMER · REG                             | gold      | Set       |

| UPCOUNTER, PRECALER 0, 1                | Run       | Cleared   |

| Serial Interface                        |           | Run *1    |

| Serial Clock                            | Hold      | Eold      |

| Interrupt Control Circuit               | Run       | Stop      |

| Interrupt Enable Flag                   | Eold      | Reset     |

| INTO, INTL Input                        | Active    | Inactive  |

| INTT                                    | ne cave   | -         |

| TS (INTES)                              | 1         | -         |

| MASK Register                           | Hold      | Set       |

| Pending Interrupts (INTFX)              | HOLD      | Reset     |

| REL Input                               | Inactive  | Active    |

| RESET Input                             | Active    | 1         |

| On-Chip RAM                             |           | Fold      |

| Output Latch in Port A, E, E            | Ī         | 1010      |

| Program Counter (PC)                    | ]         | Cleared   |

| Stack Pointer (SP)                      |           | Unkown    |

| General Registers (A, B, C, D. E, H. L) | 1         | onnown    |

| Program Status Word (FSW)               | Bold      | Reset     |

| MODE 3-Register                         | - HOIG    | Bold      |

| Stand-by Control Register (SCE-5C3)     | 1         | BUIG      |

| Stand-by Control Register (SC4)         |           | Set       |

| Timer Mode Register (1920.1)            |           | Hold      |

| Timer Mode Register (TH2)               |           | Set       |

| Serial Mode Register (SM)               |           | Bold      |

| Data Bus (DE0-7)                        | Bigh-Z    | Eigh-Z    |

| RD, WR Cutput                           | High      | Bigh      |

Note 1. Serial clock counter are running and T8 is generated, however, there are no effect by it.

Note 2. If PE is used as address bus data are retained in halt-mode-bus and forced low by stop-mode.

6. RESET OPERATION

When two sampling pulses continuously sample low level of RESET signal, the RESET signal is judged correct. The sampling signal is of 4us cycle (at 4MHz operation) in the uPD78C06 and 2.67us cycle in the uPD78C06A, respectively. Therefore, the RESET signal needs to be kept low for 8us and 5.34us, respectively in order to be recognized as a correct RESET signal in the asynchronous case. When the RESET signal is recognized (the internal Reset F/F2 is set), the program counter (PC) is cleared and the other internal circuits are initialized. Outputs of PA7  $\sim$  PA0, TO and SO become low level. RD and WR outputs become high level (respective inactive level). PB7 ~ PB0 and SCK of input/ output line become high impedance (input mode). With a delay of one clock, PE15  $\,{}^{\circ}$  PE0 become low level and DB7  $\,{}^{\circ}$ DB0 become high impedance. When high level of RESET signal is sampled, the internal Reset F/Fl is immediately reset and after one clock, the internal Reset F/F2 is reset. After further two clocks, the program starts (from address 0). However, since the address 0 is an internal ROM, neither address nor RD signal is output (uPD78C05/C05A behave in different way). The RESET signal has the priority over all control signals including interrupt.

## Fig. 6-1 Reset Timing

PE inactive

DB high impedance

Program Start

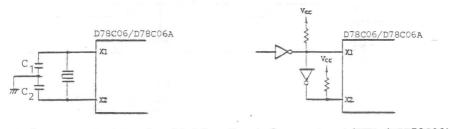

#### 7. Clock Driver Circuit

You may drive the clock input (X1, X2) of the uPD78C06/78C06A with a crystal, or an external clock source. The driving frequency must be four times the desired internal system clock frequency.

Fig. 7-1 Clock Driver Circuit

a) Crystal

b) External Source

Note:

- a) efficient reduction of power consumption (entering stop mode) only possible with internal clock.

- b) ceramic resonators can be applied, too. Please inform you at your NEC-office.

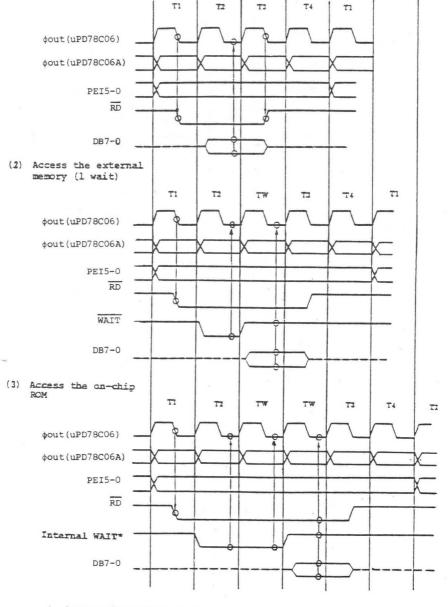

8. Bus Timing

8.1 OP Code fetch

Fig. 8-1 OP code fetch (1st or 2nd) timing

\* Two wait cycles are automatically inserted when the on-chip ROM access. 49

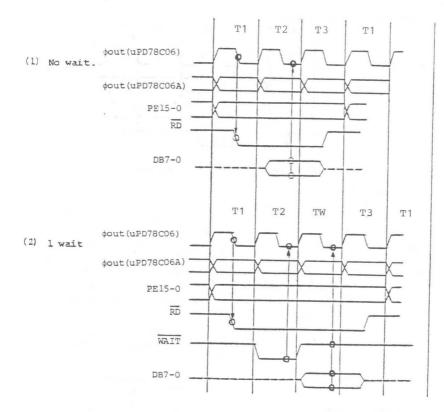

8.2 Memory read

Fig. 8-2 Memory read timing

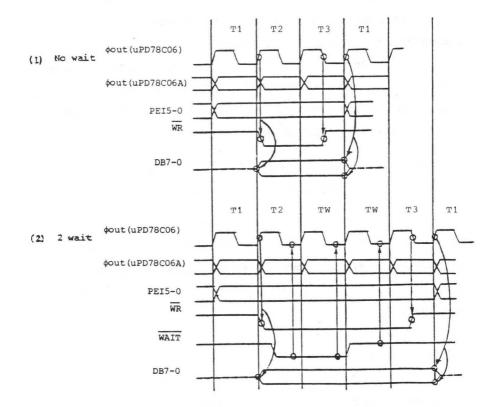

8.3 Memory write

Fig. 8-3 Memory write timing

9. String of three 'special' Instructions

When more than one certain instruction among these three occur in sequence, only the first instruction encountered will be executed. The remainder of the instructions in the string will be ignored and just be replaced with idle clocks ; they require same number of clocks as usual execution of these instructions. There are two groups of the instructions which have the above special feature, and these two groups are independent of each other.

| Group | A: | MVI | A, | byte |   |     |    |      | (L1 | Flag)  |

|-------|----|-----|----|------|---|-----|----|------|-----|--------|

| Group | в: | MVI | L, | byte | : | LXI | H. | word | (L0 | Flag). |

If there is a string of the instructions (MVI A, byte), belonging to the group A, the L0.flag is set to 1. If there is a string of the instructions (MVI L, byte and/or LX1 H, word) belonging to the group B, the L0 flag is set to 1. An interrupt is not disabled during the execution of a string of these instructions. Since the L flags are saved to the stack during an interrupt operation, the uPD78C06/78C06A can resume to execute the peculiar feature after returning from the interrupt procedure.

| $Start \longrightarrow$ | MVI | A, | 0   | ;A < 0          |      |

|-------------------------|-----|----|-----|-----------------|------|

|                         | MVI | A, | 1   | ;NOP(11CLOCKS), | Ll=1 |

|                         | MVI | A, | 2   | ;NOP(11CLOCKS), | L1=1 |

|                         | MVI | L, | OAH | ; L < 0 AH      |      |

|                         | MVI | L, | OBH | ;NOP(11CLOCKS), | L0=1 |

| Interrupt               | MVI | L, | OCH | ;NOP(11CLOCKS), | L0=1 |

|                         |     |    | 00H | ;NOP(16CLOCKS), | L0=1 |

## 10. uCOM-87LC Instruction Set

| Symbols | Descriptions              |

|---------|---------------------------|

| r       | A. B. C. D. E. H. L       |

| r l     | B, C, D, E, H, L          |

| r 2     | A, B, C                   |

| 57      | PAPB MK MB TM S TMM SM SC |

| srl     | PAPBPCMK STMM SC          |

| sr2     | PA PB PC MK               |

| rp      | SP. B. D. H               |

| rpl     | V. B. D. H                |

| гра     | B. D. H. D+, H+, D-, H-   |

| wa      | 8 bit immediate data      |

| word    | 16bic -                   |

| byte    | 8 bit                     |

| if      | F0. F1. FT. FS.           |

| £       | CY. Z                     |

10.1 Symbols/Description on Operand

(Notes)

At sr~sr2, the symbols of 'PA', 'PB', etc. stand for the following, respectively:

PA=PORTA, PB=PORTB, PC=PORTC, MK=MASK·reg, MB=MODE·B, TM=TIMER·REG, S=SERIAL I/O, TMM=TIMER MODE REG, SM= SERIAL MODE REG, SC=STANDBY CONTROL REG

2. At rp~rpl, the 'SP', 'B', etc. stand for the following, respectively:

SP=STACK POINTER, B=BC, D=DE, H=HL, V=FFH·A

At rpa, the 'B' 'D', etc. stand for the following, respectively:

B=(BC), D=(DE), H=(HL),  $D+=(DE)^+$ ,  $H+=(HL)^+$ ,  $D-=(DE)^-$ ,  $H-=(HL)^-$

At if, the 'FO', 'F1', etc. stand for the following, respectively:

F0=INTF0, F1=INTF1, FT=INTFT, FS=INTFS

At f, the 'CY', 'Z', stand for the following, respectively.

CY=CARRY, Z=ZERO

follows:

....

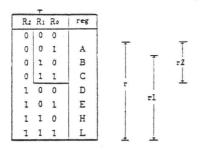

| S3  | Sz | Sı | So | special reg          |    |     |     |

|-----|----|----|----|----------------------|----|-----|-----|

| 0   | 0  | 0  | 0  | PORT A               | Ť  | Ť   | T   |

| 0   | 0  | 0  | I  | PORT B               | ST | ł   |     |

| 0   | 0  | l  | 0  | PORT C               | -  | srl | sr2 |

| 0   | 0  | 1  | I  | MASK                 | Ĩ  | N   | 1   |

| 0   | l  | 0  | 0  | MODE · B             |    | - ) |     |

| 0   | 1  | 0  | 1  | -                    |    |     |     |

| 0   | 1  | 1  | 0  | TIMER · REG          |    |     |     |

| 0   | 1  | 1  | 1  | -                    | ST | 1   |     |

| 1   | 0  | 0  | 0  | SERIAL · I/O         |    | TA  |     |

| 1 1 | 0  | 0  | 1  | TIMER MODE REG.      |    |     |     |

| 1   | 0  | 1  | 0  | SERIAL MODE REG.     |    | - / |     |

| 1   | 0  | 1  | 1  | STANDBY CONTROL REG. | Į. | E.  |     |

|     |    |    |    |                      |    |     |     |

| ъb    |          |

|-------|----------|

| P1 Po | reg-pair |

| 0 0   | SP       |

| 01    | BC       |

| 10    | DE       |

| 1 1   | HL       |

| Q1 Q0 | reg pair |

|-------|----------|

| 0 0   | FFHA     |

| 01    | BC       |

| 10    | DE       |

| 11    | HL       |

| Az | A۱ | Ae | addressing |

|----|----|----|------------|

| 0  | 0  | 0  |            |

| 0  | 0  | 1  | (BC)       |

| 0  | 1  | 0  | (DE)       |

| 0  | 1  | 1  | (HL)       |

| 1  | 0  | 0  | (DE)+      |

| 1  | 0  | 1  | (HL)+      |

| 1  | 1  | 0  | (DE)-      |

| 1  | I  | I  | (HL)-      |

| 12 | Iı | Io | INTE   |

|----|----|----|--------|

| 0  | 0  | 0  | INTF 0 |

| 0  | 0  | 1  | INTET  |

| 0  | 1  | 0  | INTF 1 |

| 0  | 1  | 1  | -      |

| I  | 0  | 0  | INTES  |

| F2 | Fı | Fe | flag |

|----|----|----|------|

| 0  | 1  | 0  | CY   |

| 1  | 0  | 0  | Z    |

TRE

| skin     | Condition  |                  |                   |                 |                  |                  |                  |                    |                |              |                    |                 |                      |                      |                            |                          |  |  |

|----------|------------|------------------|-------------------|-----------------|------------------|------------------|------------------|--------------------|----------------|--------------|--------------------|-----------------|----------------------|----------------------|----------------------------|--------------------------|--|--|

|          | Functions  | r I ⊷ A          | A←r]              | 814-Y           | A⊷sr1            | r⊷(ward)         | (word)←r         | r hyts             | (FFII. wa) + A | A+(FFII. wa) | (rpa) ↔ A          | A⊷(rpa)         | (word)←C, (word+1)←B | (word)→E. (word+1)→D | (word)←L, (word+1)←II      | (word)→SP'⊥ (word+1)→SPw |  |  |

| Clock    | Cycle      | 9                | 9                 | 14              | 14               | 25               | 25               | =                  | 14             | 14           | 6                  | 6               | 28                   | 28                   | 28                         | 28                       |  |  |

|          | 13 4       |                  |                   |                 |                  | High Adrs        | High Adrs        |                    |                |              |                    |                 | High Adra            |                      |                            |                          |  |  |

| des      | B 3        |                  |                   |                 |                  | Low Adrs         | Low Adrs         |                    |                |              |                    |                 | Low Adrs             |                      | 2.<br>1. 1. 12<br>1. A. 14 | - 3-                     |  |  |

| Op Codes | U 2        |                  |                   | 1 0 0 5 5 5 5 5 | 1 1 0 0 5,5,5,56 | 0 1 1 0 1 R.R.R. | 0 1 1 1 1 R.H.R. | Dafa               | Olfset         | ()[[sel      |                    |                 | 0011110              | 00101110             | 0 1 1 1 1 1 0              | 00001110                 |  |  |

|          | B 1        | 0 0 0 1 1 RikiRe | 0 0 0 0 1 RaRi Ro | 01001101        | 01001100         | 01110000         | 01110000         | 0 1 1 0 1 R. R. R. | 00111000       | 00101000     | 0 0 1 1 1 A: A: A. | 0 0 1 0 1 A1A1A | 01110000             |                      |                            |                          |  |  |

|          | operam     | rl, A            | A. rl             | er, A           | A, srl           | r, word          | word, r          | r, byle            | W.B.           | W.B.         | rpa                | rpa             | p.rom                | word                 | word                       | ward                     |  |  |

|          | LINCHOUTCR | MUV              | NOW               | NOM             | MOV              | MOV              | MOV              | IVM                | STAW           | TDAW         | STAX               | TDAX            | SDCD                 | SDED                 | SHLD                       | sspu                     |  |  |

| Sk i p    | ondition     |                       |                       |                       |                          |                          |                                    |                  |                  |                  |                  |                  |                    |                             |                  |                                  | No<br>Carry        | No<br>Carry     | Na<br>Barraw       | No<br>Norrow |

|-----------|--------------|-----------------------|-----------------------|-----------------------|--------------------------|--------------------------|------------------------------------|------------------|------------------|------------------|------------------|------------------|--------------------|-----------------------------|------------------|----------------------------------|--------------------|-----------------|--------------------|--------------|

|           | e directiona | C←(word), B←(word+1 ) | E←(word), D)←(word+1) | L←(word), ll←(word+1) | SPL←(word), SPn←(word+1) | (SP−1)←rplu, (SP−2)←rplt | грІ⊥'-(SP), гр⊡•-(SP+1)<br>SP+SP+2 | tp⊷word          | A←A+r            | A+-A+(rpa)       | A⊷A+r+CY         | A+-A+(rpa)+CY    | A⊷A-+              | $A \leftarrow A - (r_{pa})$ | A⊷A-r-CY         | $A \leftarrow A - (r_{pa}) - CY$ | A←A+r              | A+A+(rpa) [0    | A+A-r              | 15 A+A-(rps) |

| clock     | Cycle        | 28                    | 28                    | 28                    | 28                       | 21                       | 18                                 | 16               | 12               | 15               | 12               | İs               | 12                 | 15                          | 12               | 15                               | 12                 | 15              | 12                 | 15           |

|           | B 4          | High Adrs             |                       |                       |                          |                          |                                    |                  |                  |                  |                  |                  |                    |                             |                  |                                  |                    |                 |                    |              |

|           | B 3          | Low Adrs              |                       |                       |                          |                          |                                    | lligh Dyte       |                  |                  |                  |                  |                    |                             |                  |                                  |                    |                 |                    |              |

| Op Codes  | B 2          | 00011111              | 00101111              | 00111111              | 00001111                 | 0 0 4,4,1 1 1 0          | 0 0 9,9+1 1 1                      |                  | 1 1 0 0 0 RIRIRO | 1 1 0 0 0 VIVIA. | 1 1 0 1 0 R.H.R. | 1 1 0 1 0 AIAIA. | 1 1 1 0 0 R1 R1 R. | 1 1 1 0 0 VIV               | 1 1 1 1 0 R.R.R. | 1 1 1 1 0 A: A: A.               | 1 0 1 0 0 R: RI R. | 1 0 1 0 0 VI VI | 1 0 1 1 0 R: Rille | 10110A.A.A.  |

|           | B 1          | 01110000              |                       |                       |                          | 01001000                 | 01001000                           | 0 0 L P. O 1 0 0 | 01100000         | -                | 0                | -                | 0                  | -                           | 0                | -                                | 0                  | -               | 0                  | -            |

|           |              | 011                   |                       |                       |                          | 010                      | 010                                | 006              | 011              | 0111             | 0110             | 0111             | 0110               | 0111                        | 0110             | 0111                             | 0110               | 0111            | 0110               | 0111         |

|           | history      | p.iom                 | word                  | word                  | word                     | rp 1                     | rpl                                | rp, word         | A, r             | rpa              | Λ, Γ             | r pa             | А, г               | rpa                         | Λ, Γ             | rpa                              | Λ, Γ               | rpa             | Α, Γ               | r.p.e        |

| Hnomonica | nnenontca    | LBCD                  | LDED                  | СНГЛ                  | LSPD                     | PUSH                     | POP                                | ГХІ              | ADD              | ADDX             | ADC              | ADCX             | SUB                | SUDX                        | SBB              | SBDX                             | ADDAC              | ADDNCX          | SUBNB              | XUNNUS       |

|           |              | suo                   | rrour                 | Isal                  | NOVE                     | Dece                     | 178-91                             | :                | 1                |                  |                  | suo              | חכבק.              | IJ SU ]                     | בדָכ י           | sadt                             | Ari                |                 |                    |              |

. 57

| 0.3                   | B1 D2                 |

|-----------------------|-----------------------|

| 0 100018:R.R.         | 01100000 100018:Rigo  |

| 1 0 0 0 1 4:4:4.      | 100014:4:4.4          |

| 1 0 0 1 1 R.R. N.     | 1 0 0 1 1 R.R.N.      |

| 1 0 0 1 1 A: A: A.    | 1 0 0 1 1 A: A: A     |

| 1 0 0 1 0 R. R. R.    | 1 0 0 1 0 Rz Ri Re    |

| 1 0 0 1 0 A: A: A.    | 1 0 0 1 0 A1 A1       |

| 1 0 1 0 1 R.R.R.      | 1 0 1 0 1 R. R. R.    |

| 1 0 1 0 1 A: A: A.    | 1 0 1 0 1 A: A: A     |

| 10111R.R.R.           | 10111R2R1R0           |

| 1 0 1 1 1 A: A: A. A. | 10111A:A:A            |

| 1 1 0 0 1 A: A: A. A. | 1 1 0 0 1 A: A: A. A. |

| 1 3 0 1 1 AzAzAs      | 1 1 0 1 1 AzAzAs      |

| 111018:8.4.           | 111011114             |

| 1 1 1 0 1 A: A: A.    | 1 1 1 0 1 A: A: A.    |

| 1 1 1 1 R.R.R.        | 1 1 1 1 1 8. 6. 6.    |

| 1 1 1 1 1 AIAIA       | 111114.4.4.4          |

| 1 4 | Minimum | Owerand   |            |          |                  | Op Codes |      |     |     | Clock | Functions       | Skip         |

|-----|---------|-----------|------------|----------|------------------|----------|------|-----|-----|-------|-----------------|--------------|

|     |         | 5118 0 00 | <b>n</b> 1 |          | B 2              | 54       | 83   | -   | 134 | Cycle |                 | Condition    |

| X   | XRI     | A, byte   | 00010110   | 10       | Data-            |          |      |     |     | 13    | A←A∨byte        |              |

| V   | ADINC   | A, byte   | 0010       |          |                  |          |      |     |     | 11    | A←A+byte        | No<br>Carry  |

| 2   | SUINB   | A, byte   | 0011       |          | 2                | 0        |      |     |     | 11    | A ← Å – byte    | No<br>Borrow |

| V   | ADI     | A. byte   | 0100       |          |                  | 3        |      |     |     | 11    | A ← A + byte    |              |

| <   | ACI     | A, byte   | 1010       | 1.22<br> |                  |          |      |     |     | =     | A-A + byte + CY |              |

| 3   | sui     | A. byte   | 0110       |          |                  |          |      |     |     | =     | A-A-byte        |              |

| S   | SBI     | A. byte   | 0111       |          |                  |          |      |     |     | =     | A-A-byte-CY     |              |

| ×   | INV     | A, byte   | 00000111   | 11       |                  |          |      | - 1 |     | 11    | A⊷A∧byte        |              |

| 0   | ORI     | A. byte   | 0001       |          |                  |          |      |     |     | =     | AAV byte        |              |

| 0   | CTI     | A, byte   | 0010       |          |                  |          |      |     |     | =     | A-hyte-1        | No<br>Borrow |

| 1   | LTI     | A. hyte   | 0011       |          |                  |          |      |     |     | 11    | A-byte          | Borrow       |

| 0   | INO     | A, byte   | 0100       |          |                  |          |      |     |     | =     | AAbyle          | No Zero      |

| 0   | DFF1    | A, byte   | 0101       |          |                  |          |      |     |     | 11    | A∧byle          | Zero         |

| Z   | NEI     | A. byte   | 0110       |          |                  |          |      |     |     |       | A - byte        | No Zero      |

|     | EQI     | A. byte   | 0111       |          |                  |          |      |     |     |       | A-bye           | Zcro         |

| <   | INV     | sr2. hyte | 01100100   | 0 0      | 1 0 0 0 1 0 5150 | 0 5150   | Data |     |     | 23    | ar2⊷ar2∧byte    |              |

| 0   | ORI     | sr2, byte |            |          | 1001             |          |      |     |     | 23    | sr2-sr2Vhyte    |              |

| 0   | ONI     | sr2, byte |            |          | 1100             |          |      |     |     | 20    | ar 2 A byte     | No Zero      |

| 0   | OFFI    | sr2, byte |            |          | 1101             |          |      |     |     | 20    | sr2Abyte        | Zerb         |